MT8941B 데이터 시트보기 (PDF) - Zarlink Semiconductor Inc

부품명

상세내역

일치하는 목록

MT8941B Datasheet PDF : 27 Pages

| |||

MT8941B

Data Sheet

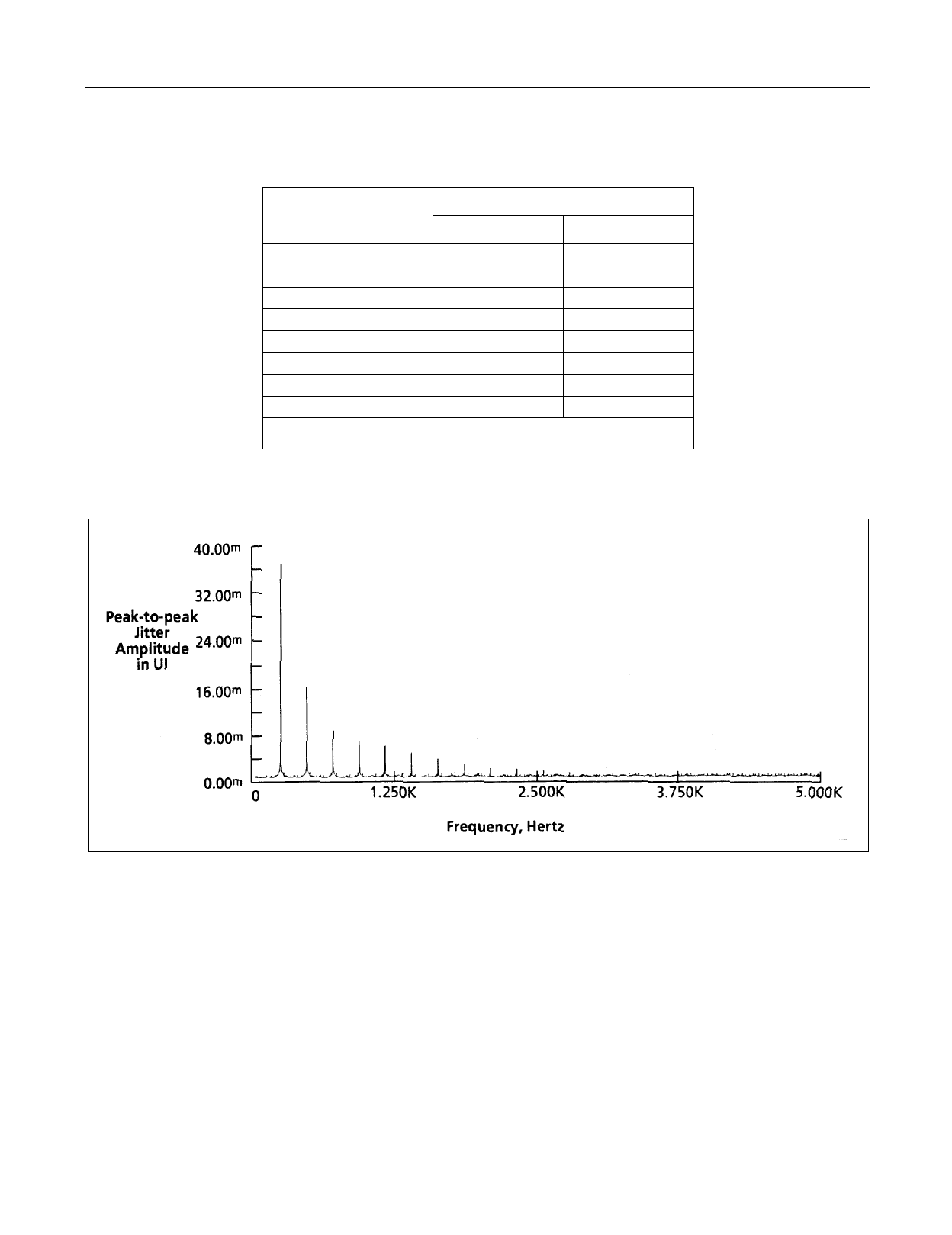

The T1 and CEPT standards specify that, for free running equipment, the output clock tolerance must be less than

or equal to ±32ppm and ±50ppm respectively. This requirement restricts the oscillators of DPLL #1 and DPLL #2

to have maximum tolerances of ±32ppm and ±50ppm respectively.

Oscillator Clock*

Tolerance (±ppm)

Lock-in Range (±Hz)

DPLL #1

DPLL #2

5

2.55

1.91

10

2.51

1.87

20

2.43

1.79

32

2.33

1.69

50

2.19

1.55

100

1.79

1.15

150

1.39

.75

175

1.19

.55

Note: * Please refer to the section on “Jitter Performance and Lock-in

Range” for recommended oscillator tolerances for DPLL #1 & #2.

Table 6 - Lock-in Range vs. Oscillator Frequency Tolerance

Figure 5 - The Spectrum of the Inherent Jitter for either PLL

10

Zarlink Semiconductor Inc.