MT8941B 데이터 시트보기 (PDF) - Zarlink Semiconductor Inc

부품명

상세내역

일치하는 목록

MT8941B Datasheet PDF : 27 Pages

| |||

MT8941B

Data Sheet

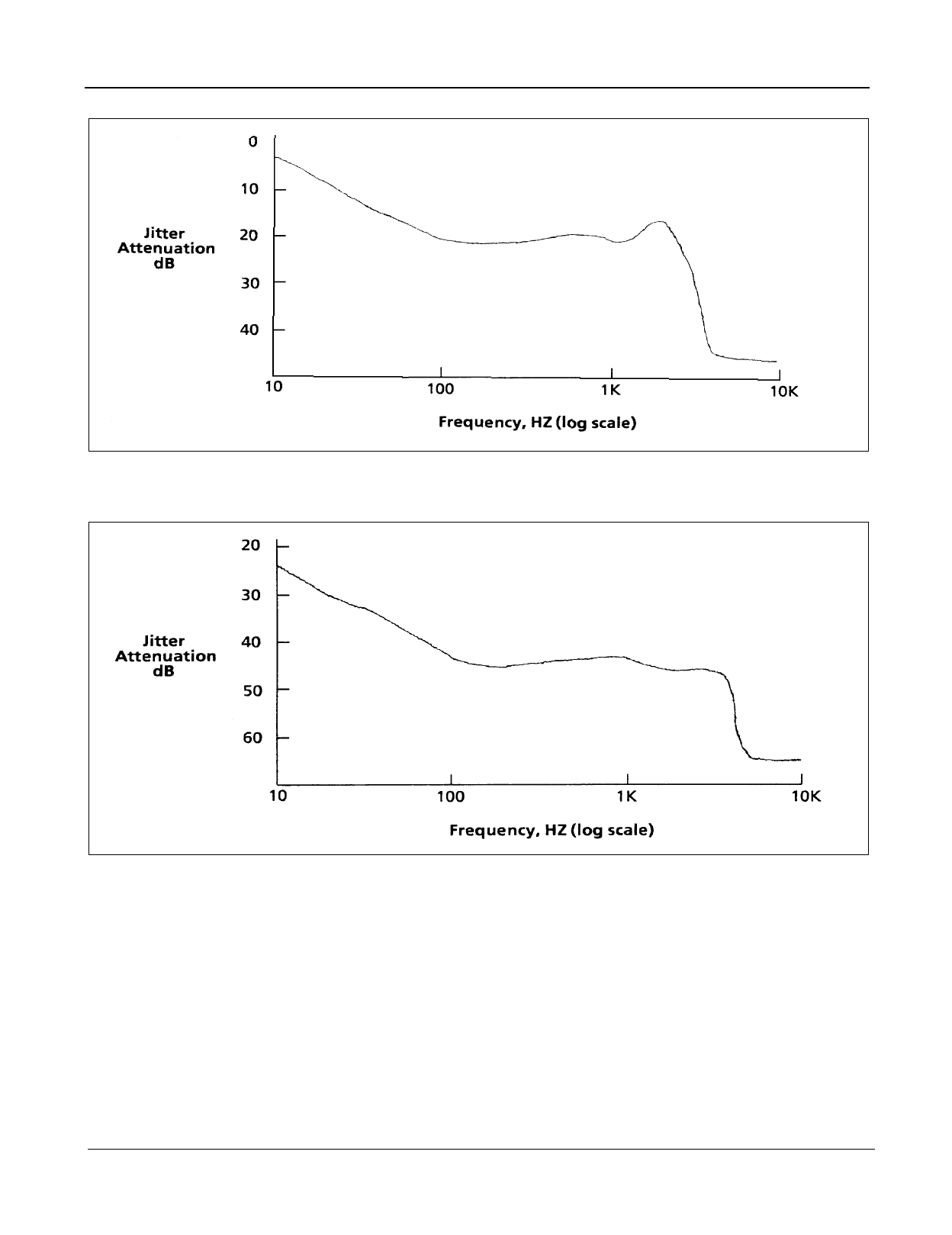

Figure 6 - The Jitter Transfer Function for PLL1

Figure 7 - The Jitter Transfer Function for PLL2

However, if DPLL #1 and DPLL #2 are daisy-chained as shown in Figures 9 and 10, the output clock tolerance of

DPLL #1 will be equal to that of the DPLL #2 oscillator when DPLL #2 is free-running. In this case, the oscillator

tolerance of DPLL #1 has no impact on its output clock tolerance. For this reason, it is recommended to use a

±32 ppm oscillator for DPLL #2 and a ±100 ppm oscillator for DPLL #1.

11

Zarlink Semiconductor Inc.