73M2910L 데이터 시트보기 (PDF) - TDK Corporation

부품명

상세내역

일치하는 목록

73M2910L Datasheet PDF : 35 Pages

| |||

DESCRIPTION

The 73M2910L high performance micro-controller is

based on the industry standard 8-bit 8032

implemented in an advanced submicron CMOS

process. The processor has the attributes of the

8032, including instruction cycle time, UART, timers,

interrupts, 256 bytes of on-chip RAM and

programmable I/O. The architecture has been

optimized for low power portable modem or

communication applications by integrating unique

features with the core CPU.

A key feature is a user friendly HDLC Packetizer,

accessed through the special function registers. It

has a serial I/O, hardware support for 16 and 32-bit

CRC, zero insert/delete control, a dedicated interrupt

and a clear channel mode for by-passing the

packetizer.

Other features include additional user programmable

I/O with programmable bank select and chip select

logic, designed to eliminate board level glue logic. It

also includes two general-purpose input ports with

programmable wakeup capability.

For devices that require non-multiplexed address

and data buses, eight latched outputs for the low

byte of the address are available.

(continued)

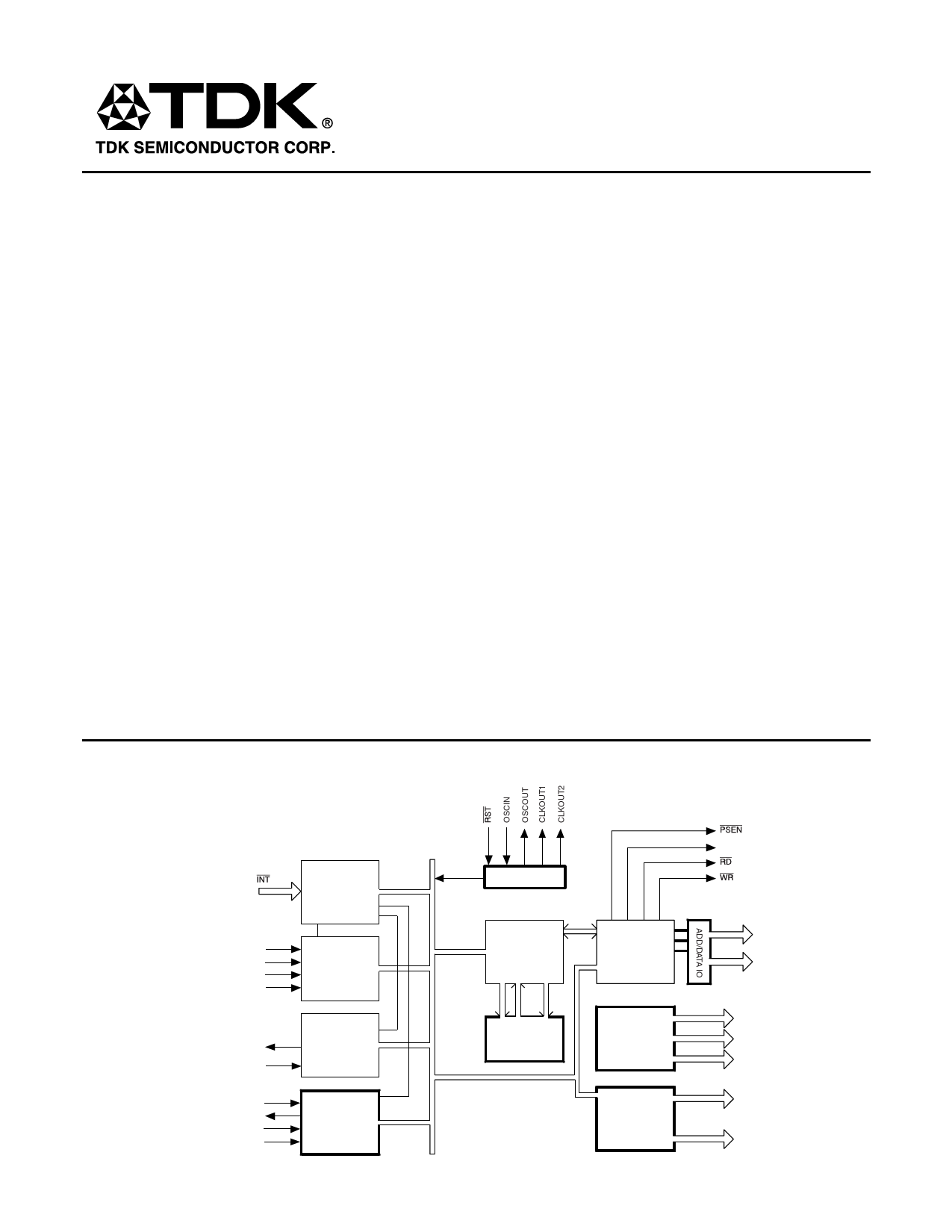

BLOCK DIAGRAM

73M2910L

Microcontroller

April 2000

FEATURES

• 8032 compatible instruction set

• 44 MHz Operation from 3.3 to 5.5V

• HDLC support logic (Packetizer, 16 and 32

CRC, zero ID)

• 24 pins for user programmable I/O ports

• 8 pins programmable chip select logic or I/O

for memory mapped peripheral eliminating

glue logic

• 3 external interrupt sources (programmable

polarity)

• 16 dedicated latched address pins

• Multiplexed data/address bus

• Instruction cycle time identical to 8032

• Buffered oscillator (or OSC/2) output pin

• 1.8432 MHz UART clock available

• Bank select circuitry to support up to 128k of

external program memory

• Also available in 100-Lead QFP and 100-Pin

PGA packages

(2:0)

INTERRUPT

CONTROL

USR 1.0

USR 1.1

USR 1.2

USR 1.3

TIMERS

RXD

TXD

PTXCLK

PTXD

PRXCLK

PRXD

UART

HDLC

TIME GEN

CPU

SFR BUS

RAM 256 X 8

ALE

MEM I/O CTRL

A (15:0)

D (7:0)

USR I/O

USR5 (1:0)

CSB (7:0)

USR3 (7:0)

USR I/O

USR2 (7:0)

USR1 (7:0)