MC33689 데이터 시트보기 (PDF) - Motorola => Freescale

부품명

상세내역

일치하는 목록

MC33689 Datasheet PDF : 18 Pages

| |||

Freescale SMeC3m36i8c9onductor, Inc.

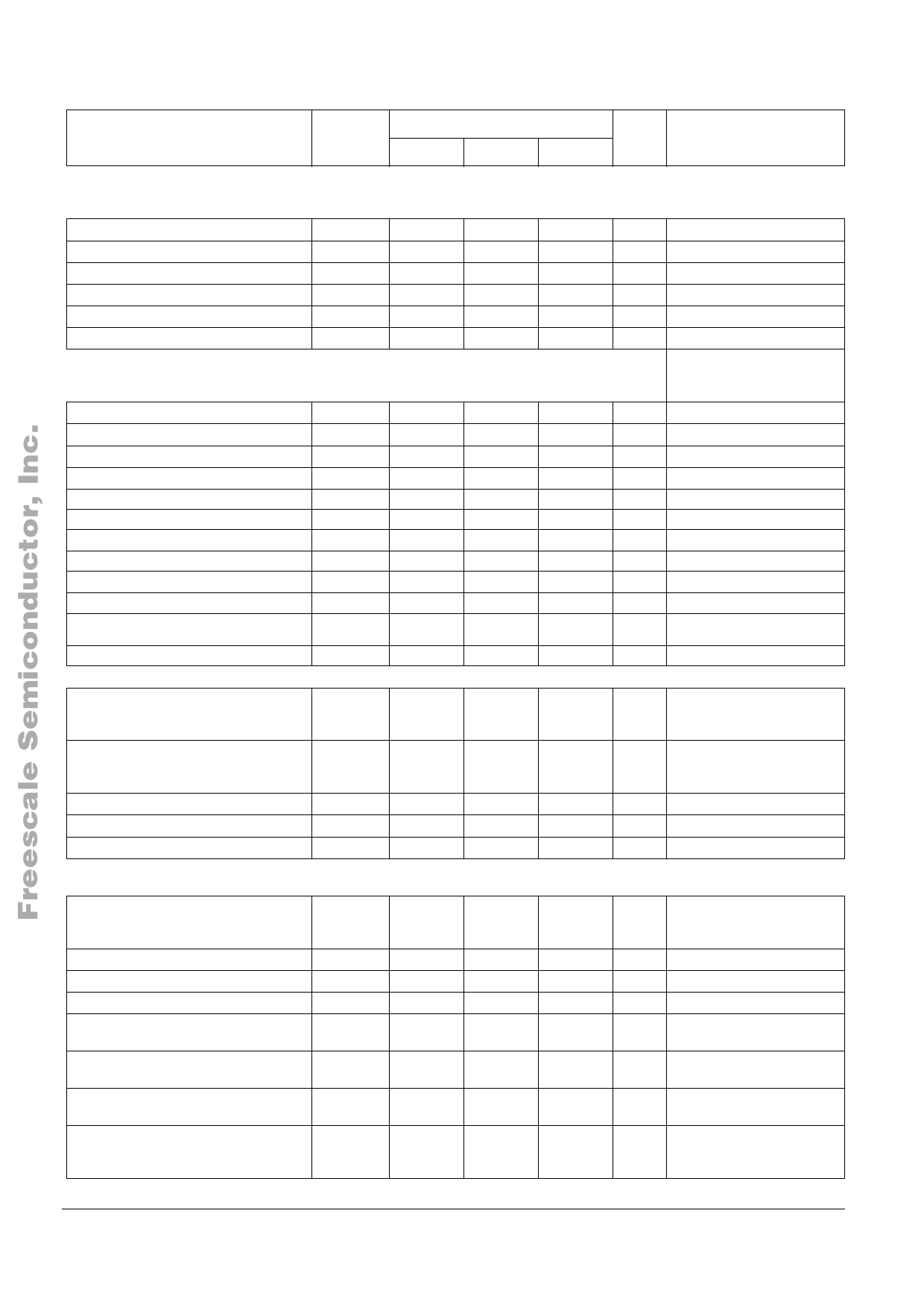

(Vs1 and Vs2 from 5.5V to 18V and Tamb from -40°C to 125°C unless otherwise noted)

Description

Symbol

Characteristics

Unit

Min

Typ

Max

note 1: when over temperature occurs, switch is turned off and latched off. Flag is set in SPI.

HS3: High side output pin

Rdson at Tj=25°C, and Iout -50mA

Ron25

7

Rdson at Ta=125°C, and Iout -50mA

Ron125

10

Rdson at Ta=125°C, and Iout -30mA

Ron3

14

Output current limitation

Ilim

60

100

200

Over temperature Shutdown

Ovt

155

190

Leakage current

Ileak

10

note 1: when over temperature occurs, switch is turned off and latched off. Flag is set in SPI

Ohms

Ohms

Ohms

mA

°C

uA

SENSE CURRENT AMPLIFIER SECTION:

Rail to rail input voltage

Output voltage range

Vimc

-0.1

Vout1

0.1

Output voltage range

Vout2

0.3

Input bias current

Input offset current

Ib

Io

-100

Input offset voltage

Vio

-15

Supply voltage rejection ratio

Common mode rejection ratio

Gain bandwidth

SVR

60

CMR

70

GBP

1

Slew rate

SR

0.5

Phase margin

PHMO

40

Vcc+0.1

Vcc-0.1

Vcc-0.3

250

100

15

V

V

V

nA

nA

mV

dB

dB

Mhz

V/us

°

Open loop gain

L1, L2 inputs

Negative Switching Threshold

Positive Switching Threshold

Hysteresis

Input current

Wake up Filter Time

OLG

85

dB

Vthn

2

2.5

3

V

2.5

3

3.5

2.7

3.2

3.7

Vthp

2.7

3.3

3.8

V

3

4

4.5

3.5

4.2

4.7

Vhyst

0.5

1.3

V

Iin

-10

10

uA

Twuf

8

20

38

us

Conditions

Vsup>9V

Vsup>9V

5.5<Vsup<9V

note 1

Output current +- 1mA

Output current +-5 mA

Guaranteed by design

Guaranteed by design

Guaranteed by design

For gain=1,load 100pF//

5kohms. Guaranteed by design

Guaranteed by design

5.5V<Vsup<6V

6V<Vsup<18V

18V<Vsup<27

5.5V<Vsup<6V

6V<Vsup<18V

18V<Vsup<27

5.5V<Vsup<27

-0.2V < Vin < 40V

Guaranteed by design

STATE MACHINE TIMING

Delay between CSB low to high transition Tstop-m

1.4

(at end of SPI stop command) and Stop Tstop-nw

6

mode activation (Guaranteed by design) Tstop-M

12

5

us

Minimum Watchdog period

30

us

No watchdog selected

50

us

Maximum watchdog period

Interrupt low level duration

Tint

7

10

13

us

Internal oscillator frequency accuracy

Osc-f1

-35

35

%

All modes, for info only

Normal request mode time out

NRtout

97

150

205

ms

Normal request mode

Delay between SPI command and HS1,

HS2 or HS3 turn on (note 1, 2)

Ts-HSon

20

us

Normal mode

Vsup>9V, Vhs >= 0.2 Vs1

Delay between SPI command and HS1,

HS2 or HS3 turn off (note 1, 2)

Ts-HSoff

20

us

Normal mode

Vsup>9V, Vhs <= 0.8 Vs1

Delay between Normal Request and Nor-

mal mode, after W/D trigger command

Ts-NR2N

6

35

30

us

Normal request mode, Guar-

anteed by design

Delay between CSB wake up (CSB low

to high) and SBC normal request mode

Tw-csb

15

40

80

us

SBC in stop mode

(Vdd1 on & reset high)

MC33689

7

For More Information On This Product,

Go to: www.freescale.com