GF9105A 데이터 시트보기 (PDF) - Unspecified

부품명

상세내역

일치하는 목록

GF9105A Datasheet PDF : 37 Pages

| |||

DATA PORT ENABLE

DP_EN is used for synchronously enabling and disabling the bi-directional data ports of the GF9105A. When DP_EN is set

high, the data ports are disabled and set to a high impedance state. When DP_EN is set low, all data ports are enabled.

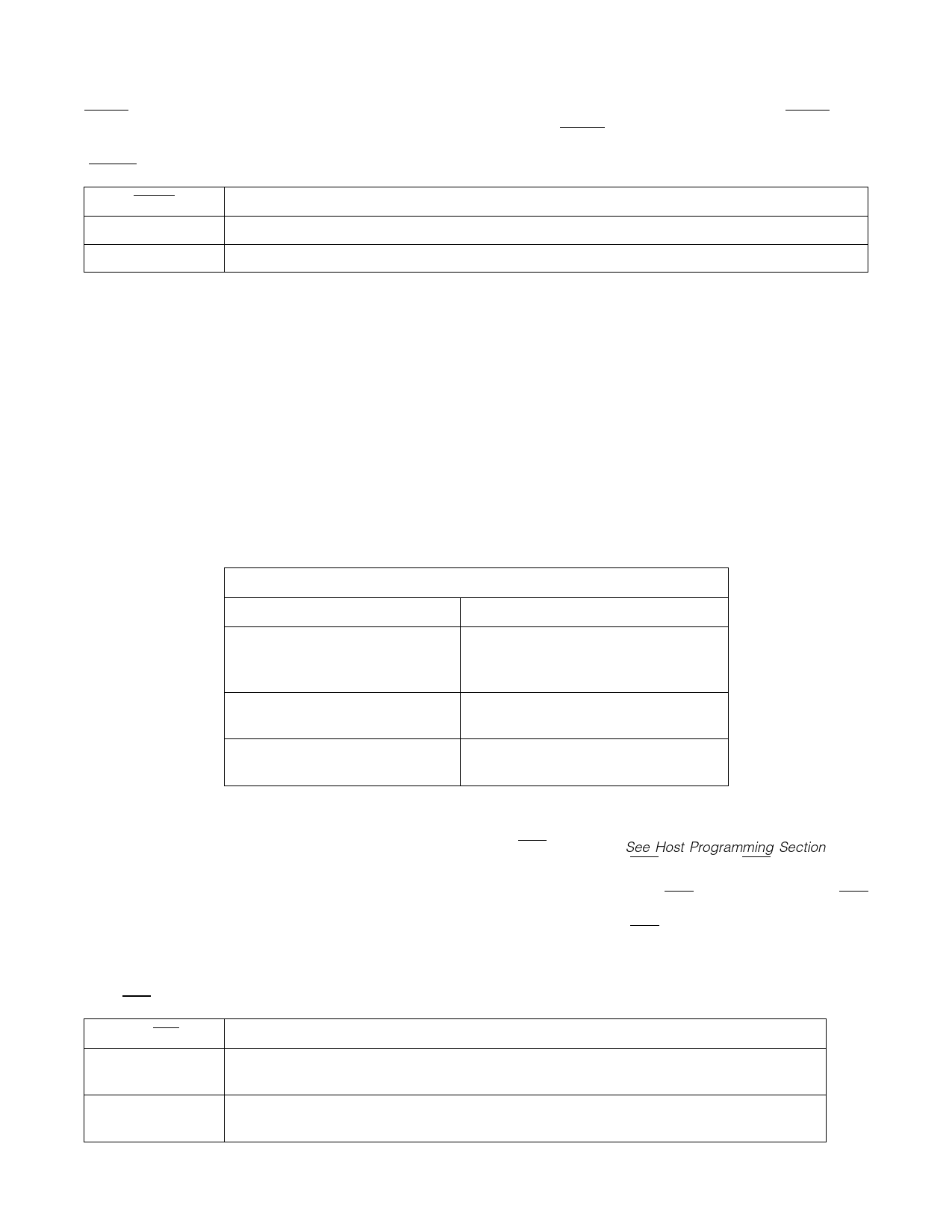

DP_EN CONTROL PIN

DP_EN

DESCRIPTION

0

Output data ports enabled.

1

Output data ports disabled (high impedance state).

INPUT CLOCK (CLK)

For standard video signals, the clock input (CLK) of the GF9105A runs at one of three rates: 13.5/18MHz, 27/36MHz or

54MHz. The 18 MHz and 36 MHz variations on main clock frequencies are used in 16 x 9 video applications where luminance

is sampled at 18 MHz. The use of a 27/36MHz clock with the GF9105A is the most common application. These clocks can be

used with any format of input or output data with the exception of single link mode. Figures 7a and 7c show multiplexed and

non-multiplexed input data with a 27/36MHz clock. When the GF9105A is used with either SMPTE RP174 compliant single link

input or output data, the input clock must run at 54 MHz (see Figure 7b).

A 13.5/18 MHz input clock speed can only be used when both the input and output data are in a non multiplexed format (see

Figure 7d). This clock rate was added to the GF9105A for use when the device is operating with non-multiplexed input and

output data, since in this case a 27.0MHz clock may not be available. To use the 13.5 MHz input clock rate, the LOWF control

bit must be set HIGH. When input clock rates of 27.0 MHz or 54.0 MHz are used, the LOWF control bit must be set LOW.

Please note, when using the GF9105A with non-multiplexed 4:2:2:4 or 4:4:4:4 input data and an input clock rate of 27/36MHz,

two rising edges of the 27/36MHz input clock are required to latch in a 13.5/18MHz input data rate (see Figure 7c).

INPUT CLOCK SUMMARY

INPUT CLOCK RATE (MHz)

MODES

13.5/18 MHz

Non-multiplexed Input Data

AND

Non-multiplexed Output Data (LOWF=1)

27/36 MHz

All Input / Output Data Formats

EXCEPT Single Link

54 MHz

SMPTE RP174 Single Link Input

OR Output Data

BASIC OPERATION OF THE GF9105A

The basic operating mode for the GF9105A is selected via the INT/DEC control bit (See Host Programming Section). The

effective block diagram of the GF9105A Processing Core depends on the state of INT/DEC. When INT/DEC is set high, the

internal FIR filters are set for interpolation and are placed in front of the programmable 3X3 color space converter. Refer to

Figures 5a and 5c for a functional block diagram of the GF9105A processing core when INT/DEC is set high. When INT/DEC

is set low, the internal FIR filters are set for decimation and are placed after the programmable 3X3 color space converter.

Refer to Figures 5b and 5d for a functional block diagram of the GF9105A with INT/DEC set low. In these figures, static

control bits (signals loaded via the asynchronous parallel interface) are shown at the top of the diagram and control signals

with dedicated input pins are shown at the bottom of the diagram.

INT/DEC CONTROL BIT

INT/DEC

DESCRIPTION

0

FIR filters set for decimation.

FIR filters placed after the 3X3 multiplier as in Figure 5b and 5d.

1

FIR filters set for interpolation.

FIR filters placed before the 3x3 multiplier as in Figure 5a and 5c.

9

521 - 88 - 03