AN-136 데이터 시트보기 (PDF) - Integrated Device Technology

부품명

상세내역

일치하는 목록

AN-136 Datasheet PDF : 12 Pages

| |||

A NEW GENERATION OF TAG SRAMS—THE IDT71215 AND IDT71216

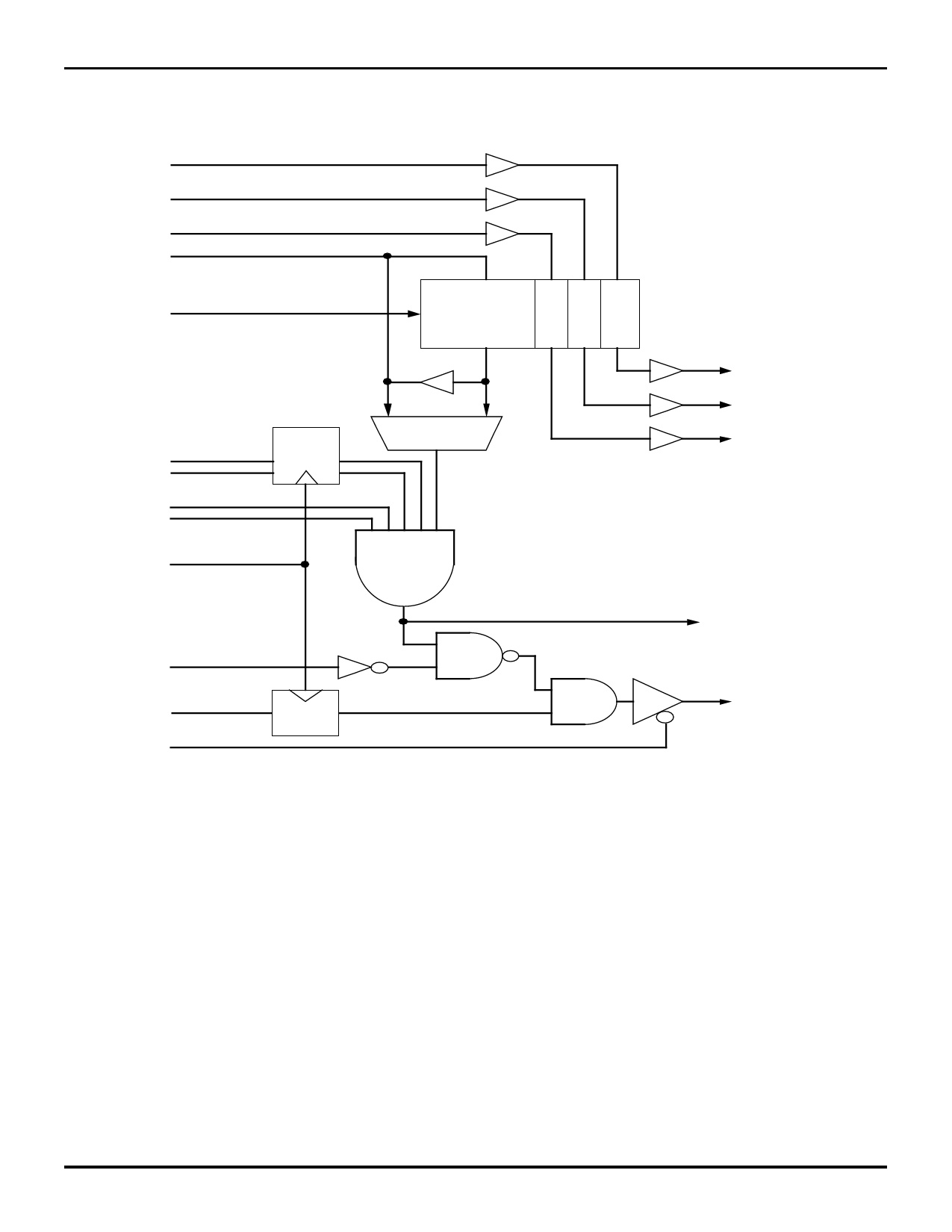

BRDY and Match logic (Generic Status bit mode)

TA names added for ap note

APPLICATION NOTE AN-136

WTIN / S3IN

DTYIN / S2IN

VLDIN / S1IN

TAG

ADDRESS

MEMORY

V D WP

WET

WES

internal RESET

OE

CLK

COMPARE

WTOUT / S3OUT

DTYOUT / S2OUT

VLDOUT / S1OUT

MATCH

BRDYH (TAH)

BRDYIN (TAIN)

BRDY (TA)

BRDYOE (TAOE)

Figure 6. Generic Mode Logic (71216 pin names are in parenthesis)

3176 drw 06

The status bits are accessed through separate input pins

and output pins. This avoids the need for fast turn around on

this bus as in the following example: a single word write hit to

a write back line results in the need to set the state to dirty (also

called “modified”). The status memory must go from reading

to writing then back to reading in as little as two cycles. If

common I/O is preferred, the user may tie the respective input

and output pins together. The status memory control signals

(WES and OES) are equivalent to WET and OET for the tag

memory. Also, because the status field is separate I/O, OES

is normally tied to VSS to permanently enable the status

outputs.

The tag and status memories are controlled independently

since normal operation of the 71215/16 finds the tag memory

in match mode and the status memory in read mode. Often,

however, WET and WES are tied together in a design because

the write function tends to be common between them. For

those times when only the status bits need to be updated,

WET, WES and OET can be asserted together without having

to externally drive the TAG bus. This causes the data read

from the tag field to be written back to the same address,

resulting in no change to the tag data.

Note that there is only one address register that is used by

both memory segments. The address is registered when

either WET or WES is sampled low, and is flow-through when

both WET and WES are sampled high.

The entire status memory is cleared to zeros when RESET

is sampled low on at least one rising edge of CLK. This can

be used to put the cache into a known state after power up, or

after a cache flush. Since reset is a type of write, WET and

WES are required to be high during reset. PWRDN must also

be high, but the state of the chip select inputs does not matter.

During reset, BRDY/TA is driven high, and MATCH is driven

low.

MATCH, BRDY AND TA

As mentioned earlier, the 71215/16 is in match mode when

OET is high and WET is sampled high. This allows the TAG0

6