MK5027(2003) 데이터 시트보기 (PDF) - STMicroelectronics

부품명

상세내역

일치하는 목록

MK5027 Datasheet PDF : 19 Pages

| |||

MK5027

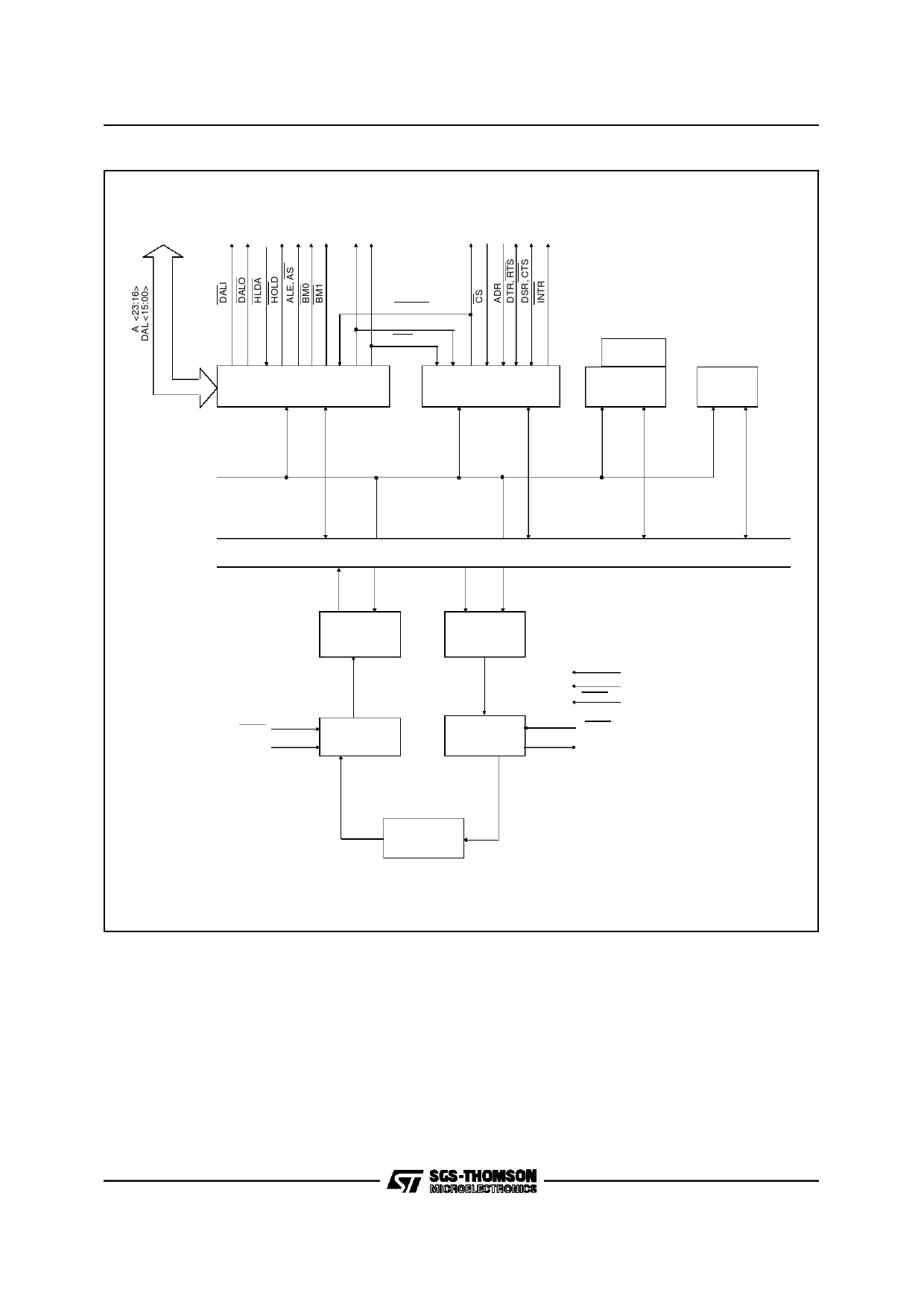

Figure 3: MK5027 Simplified Block Diagram.

DMA

CONTROLLER

READY

READ

DAS

CONTROL / STATUS

REGISTERS 0 - 5

FIRMWARE

ROM

MICRO

CONTROLLER

TIMERS

SYSCLK

RCLK

RD

INTERNAL BUS

RECEIVER

FIFO

RECEIVER

TRANSMITTER

FIFO

TRANSMITTER

VCC

VSS - GND

RESET

TCLK

TD

LOOPBACK

TEST

OPERATIONAL DECRIPTION

The SGS-THOMSON Signalling System #7 Sig-

nalling Link Controller (MK5027) device is a VLSI

product intended for data communication applica-

tions requiring SS7 link level control. The MK5027

will perform all frame formatting, such as: frame

delimiting with flags, FCS generation and detec-

tion. It will also perform all error recovery and link

control. The MK5027 also includes a buffer man-

agement mechanism that allow the user to trans-

mit and/or receive multiple MSU’s. Contained in

the buffer management is an on-chip dual chan-

6/19

nel DMA: one channel for receive and one chan-

nel for transmit. The MK5027 handles error recov-

ery and link status signalling.

The MK5027 is intended to be used with any

popular 16 or 8 bit microprocessor. Possible sys-

tem configuration for the MK5027 is shown in Fig-

ure 2. The MK5027 will move multiple blocks of

receive and transmit data directly into and out of

memory through the host’s bus. An I/O accelera-

tion processor in Figure 2 is recommended, but

not required.