MK5027(2003) 데이터 시트보기 (PDF) - STMicroelectronics

부품명

상세내역

일치하는 목록

MK5027 Datasheet PDF : 19 Pages

| |||

®

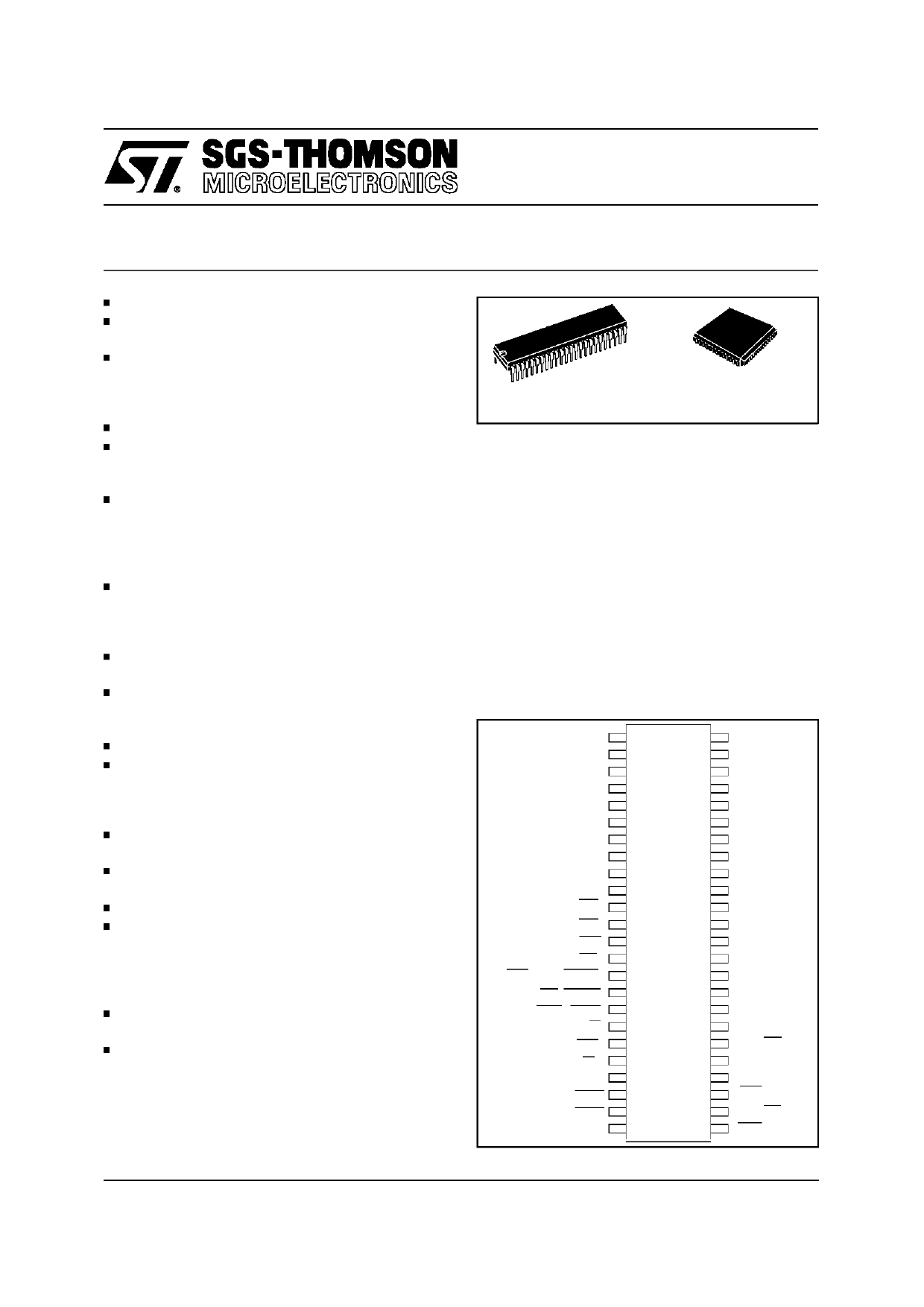

MK5027

SS7 SIGNALLING

LINK CONTROLLER

CMOS

FULLY COMPATIBLE WITH BOTH 8 OR 16

BIT SYSTEMS

SYSTEM CLOCK RATE TO 10MHz. DATA

RATE UP TO 2.5Mbps FOR SS7 PROTOCOL

PROCESSING,7Mbps FOR TRANSPARENT

HDLC MODE

COMPLETE LEVEL 2 IMPLEMENTATION

COMPATIBLE WITH 1988 CCITT, AT&T,

ANSI, AND BELLCORE SIGNALLING SYS-

TEM NUMBER 7 LINK LEVEL PROTOCOLS

52 PIN PLCC AND 48-PIN DIP PIN-FOR-PIN

COMPATIBLE WITH THE SGS-THOMSON

X.25 CHIP (MK5025) AND NEARLY PIN-FOR-

PIN COMPATIBLE WITH THE SGS-THOM-

SON VLANCE CHIP (MK5032)

BUFFER MANAGEMENT INCLUDES:

- Initialization Block

- Separate Receive and Transmit Rings

- Variable Descriptor Ring and Window Sizes.

ON CHIP DMA CONTROL WITH PROGRAM-

MABLE BURST LENGTH

SELECTABLE BEC OR PCR RETRANSMIS-

SION METHODS, INCLUDING FORCED RE-

TRANSMISSION FOR PCR

HANDLES ALL 7 SS7 TIMERS

HANDLES ALL SS7 FRAME FORMATTING:

- Zero bit insert and delete

- FCS generation and detection

- Frame delimiting with flags

PROGRAMMABLE MINIMUM SIGNAL UNIT

SPACING (number of flags between SU’s)

HANDLES ALL SEQUENCING AND LINK

CONTROL

SELECTABLE FCS OF 16 OR 32 BITS.

TESTING FACILITIES:

- Internal Loopback

- Silent Loopback

- Optional Internal Data Clock Generation

- Self Test

ALL INPUTS AND OUTPUTS ARE TTL COM-

PATIBLE

PROGRAMMABLE FOR FULL OR HALF DU-

PLEX OPERATION

DESCRIPTION

The SGS-THOMSON Signalling System #7 Sig-

nalling Link Controller (MK5027) is a VLSI semi-

September 2003

DIP48

PLCC52

conductor device which provides a complete link

control function conforming to the 1988 CCITT

version of SS7. This includes frame formatting,

transparency (so called "bit-stufling"), error recov-

ery by two types of retransmission, error monitor-

ing, sequence number control, link status con-

trol, and FISU generation. One of the outstanding

features of the MK5027 is its buffer management

which includes on-chip DMA. This feature allows

users to handlq multiple packets of receive and

transmit data at a time. (A conventional data link-

control chip plus a separate DMA chip would han-

dle data for only a single block at a time.) The

MK5027 may be used with any of several popular

16 and 8 bit microprocessors, such as 68000,

6800, Z8000, Z80, LSI-11, 8086, 8088, 8080, etc.

Figure 1: Pin Connection.

VSS-GND

DAL07

DAL06

DAL05

DAL04

DAL03

DAL02

DAL01

DAL00

READ

INTR

DALI

DALO

DAS

BMO, BYTE, BUSREL

BMI, BUSAKO

HOLD, BUSRQ

ALE, AS

HLDA

CS

ADR

READY

RESET

VSS-GND

1

48

2

47

3

46

4

45

5

44

6

43

7

42

8

41

9

M

40

10

K

39

11

5

38

12

37

13

0

36

14

H

35

15

34

2

16

33

17

5

32

18

31

19

30

20

29

21

28

22

27

23

26

24

25

VCC (+5V)

DAL08

DAL09

DAL10

DAL11

DAL12

DAL13

DAL14

DAL15

A16

A17

A18

A19

A20

A21

A22

A23

RD

DSR, CTS

TD

SYSCLK

RCLK

DTR, RTS

TCLK

1/19