IDT72510L25J 데이터 시트보기 (PDF) - Integrated Device Technology

부품명

상세내역

일치하는 목록

IDT72510L25J

IDT72510L25J Datasheet PDF : 32 Pages

| |||

IDT72510, IDT72520

BUS MATCHING BIDIRECTIONAL FIFO

COMMERCIAL TEMPERATURE RANGE

PORT A RESOURCES

CSA A1 A0

Read

Write

0

0

0

B→A FIFO

A→B FIFO

0

0

1 9-bit Bypass Path 9-bit Bypass Path

0

1

0

Configuration

Registers

Configuration

Registers

0

1

1

Status Register Command Register

1XX

Disabled

Disabled

2669 tbl 03

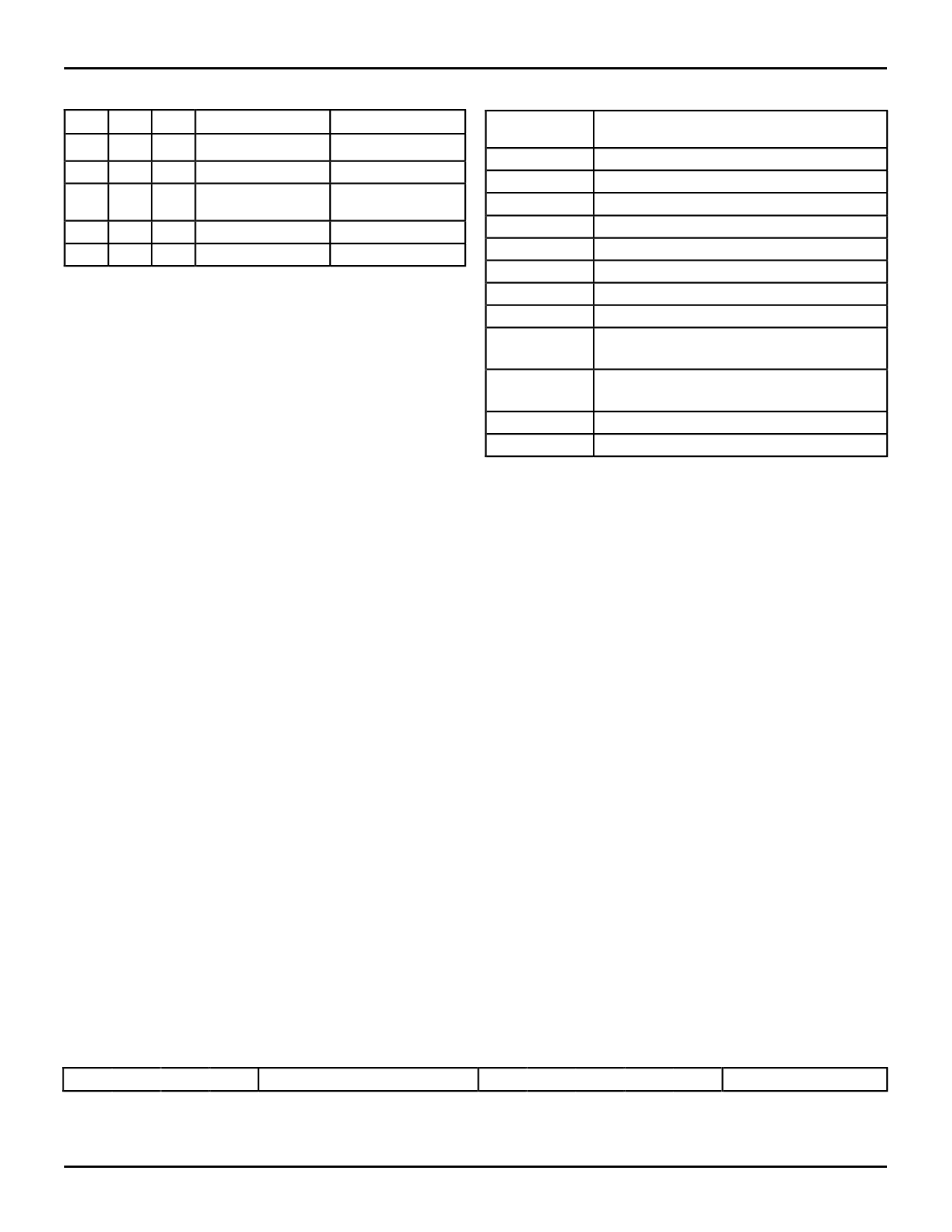

Table 1. Accessing Port A Resources Using CSA, A0, and A1

Bypass Path

The bypass path acts as a bidirectional bus transceiver

directly between Port A and Port B. The direct connection

requires that the Port A interface pins are inputs and the Port

B interface pins are outputs. The bypass path is 9 bits wide in

an 18- to 9-bit configuration or in a 36- to 9-bit configuration.

Only in the 36- to 18-bit configuration is the bypass path 18 bits

wide.

During bypass operations, the BiFIFOs must be pro-

grammed into peripheral interface mode. Bit 10 of Configura-

tion Register 5 (see Table 11) is set to 1 for peripheral interface

mode. In a 36- to 9-bit configuration, both Port B data buses

will be active. Data written into Port A will appear on both

master and slave Port B buses concurrently. To avoid Port B

bus contention, the data on DA0-DA7 and DA16 of both BiFIFOs

should be exactly the same. Data read from Port A will appear

on pins DA0-DA7 and DA16 of both BiFIFOs within the same 36-

bit word.

Command Register

Ten registers are accessible through Port A, a Command

Register, a Status Register, and eight Configuration Registers.

The Command Register is written by setting CSA = 0, A1 =

1, A0 = 1. Commands written into the BiFIFO have a 4-bit

opcode (bit 8 – bit 11) and a 3-bit operand (bit 0 – bit 2) as

shown in Figure 5. The commands can be used to reset the

BiFIFO, to select the Configuration Register, to perform intel-

ligent reread/rewrite, to set the Port B DMA direction, to set the

Status Register format, to modify the Port B Read and Write

Pointers, and to clear Port B parity errors. The command

opcodes are shown in Table 2.

The reset command initializes different portions of the

BiFIFO depending on the command operand. Table 3 shows

the reset command operands.

The Configuration Register address is set directly by the

command operands shown in Table 4.

Intelligent reread/rewrite is performed by changing the Port

B Read Pointer with the Reread Pointer or by changing the

COMMAND OPERATIONS

Command

Opcode

Function

0000

Reset BiFIFO (see Table 3)

0001

Select Configuration Register (see Table 4)

0010

Load Reread Pointer with Read Pointer Value

0011

Load Rewrite Pointer with Write Pointer Value

0100

Load Read Pointer with Reread Pointer Value

0101

Load Write Pointer with Rewrite Pointer Value

0110

Set DMA Transfer Direction (see Table 5)

0111

Set Status Register Format (see Table 6)

1000

Increment in byte for A→B FIFO Read Pointer

(Port B)

1001

Increment in byte for B→A FIFO Write Pointer

(Port B)

1010

Clear Write Parity Error Flag

1011

Clear Read Parity Error Flag

2669 tbl 04

Table 2. Functions Performed by Port A Commands

Port B Write Pointer with the Rewrite Pointer. No command

operands are required to perform a reread/rewrite operation.

When Port B of the BiFIFO is in peripheral mode, the DMA

direction is controlled by the Command Register. Table 5

shows the Port B read/write DMA direction operands.

The BiFIFO supports two Status Register formats. Status

Register format 1 gives all the internal flag status, while Status

Register format 0 provides the data in the Odd Byte Register.

Table 6 gives the operands for selecting the appropriate

Status Register format. See Table 8 for the details of the two

Status Register formats.

Two commands are provided to increment the Port B Read

and Write Pointers in case reread/rewrite is performed.

Incrementing the pointers guarantees that pointers will be on

a word boundary when an odd number of bytes is transmitted

through Port B. No operands are required for these commands.

When parity check errors occur on Port B, a clear parity

error command is needed to remove the parity error. There are

no operands for these commands.

Reset

The IDT72510 and IDT72520 have a hardware reset pin

(RS) that resets all BiFIFO functions. A hardware reset re-

quires the following four conditions: RB and WB must be HIGH,

RER and REW must be HIGH, LDRER and LDREW must be

LOW, and DSA must be HIGH (Figure 9). After a hardware

reset, the BiFIFO is in the following state: Configuration

Registers 0-3 are 0000H, Configuration Register 4 is set to

COMMAND FORMAT

15

12

11

87

3

2

0

X

X

X

X

Command Opcode

X

X

X

X

X

Command Operand

Figure 5. Format for Commands Written into Port A

2669 tbl 05

5.31

10