NJU3101 데이터 시트보기 (PDF) - Japan Radio Corporation

부품명

상세내역

일치하는 목록

NJU3101 Datasheet PDF : 22 Pages

| |||

NJU3101

PRELIMINARY

4-BIT SINGLE CHIP TINY CONTROLLER

s GENERAL DESCRIPTION

The NJU3101 is the C-MOS 4-bit Single Chip Tiny

Controller consisting of the 4-bit CPU Core, Input / Output

Selectable I/O ports, Program ROM, Data RAM, and

Oscillator Circuit (CR or Ceramic or X'tal). It is packaged

in 16-pin package (DIP or DMP form). Therefore it

provides a cost and space effective replacement with only

few external components for control-logic circuit using

standard logic ICs (i.e. 74HC) or other small controllers.

The NJU3101 is suitable for battery operated

appliances because of low operating current, wide

operating voltage range, and STANDBY function (HALT

mode).

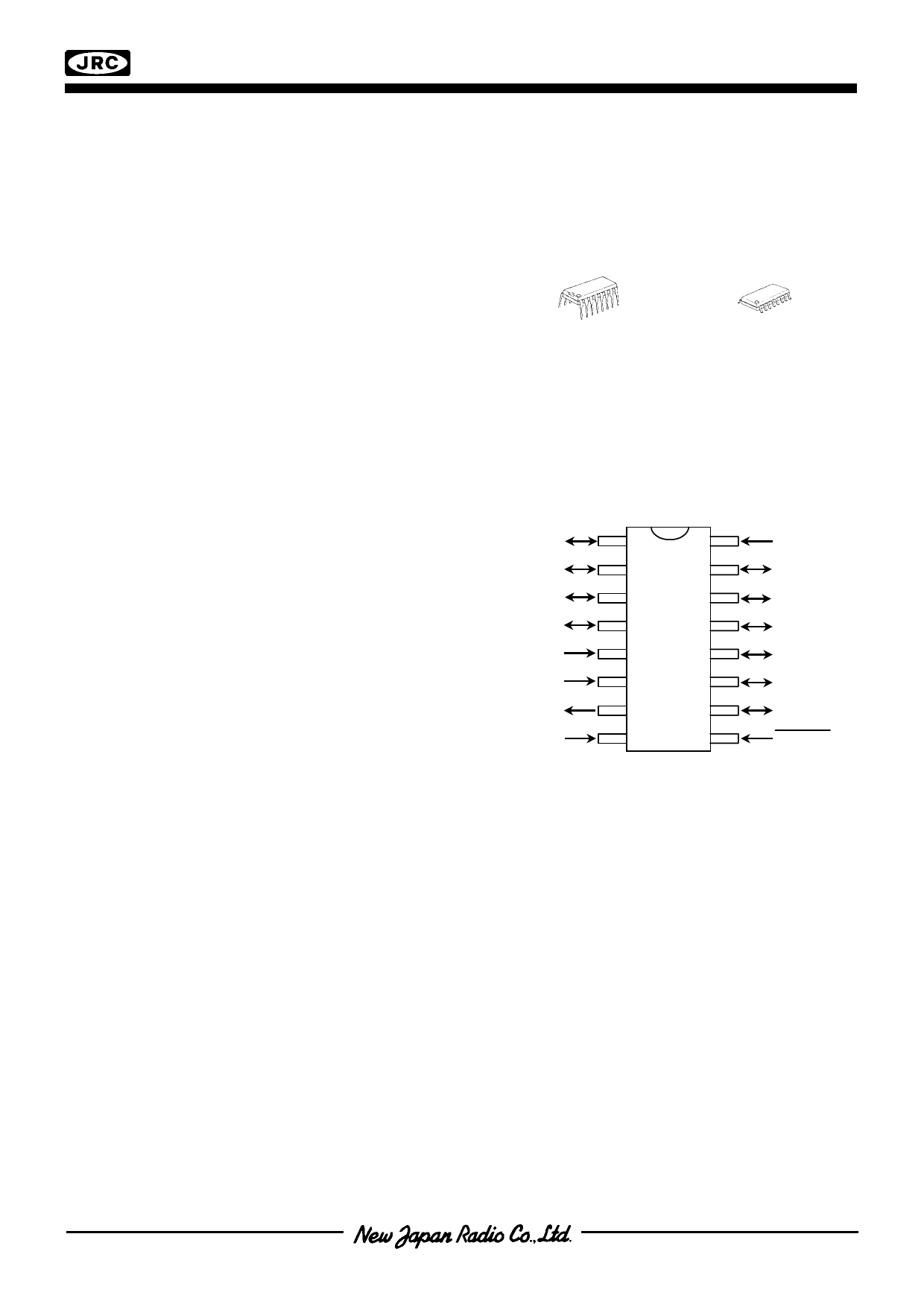

s PACKAGE OUTLINE

NJU3101D

NJU3101M

s FEATURES

s PIN CONFIGURATION

q Internal Program ROM 512 X 8 bits

q Internal Data RAM

16 X 4 bits

q Input / Output Port

10 lines

PA0

(Input / Output direction of each PORT is selected by the

mask option.)

PA1

q High Output Current terminal (2 lines)

PA2

N-Channel FET Open Drain Type (IOL)

15mA at VDD=5V

q Instruction Set

58 instructions

q Subroutine Nesting

8 levels

q Pulse Edge Detector

PA3

TEST

OSC1

The rising or falling edge of a pulse is selected by the mask OSC2

option.

q Instruction Executing Time

6/fOSC sec

VSS

q Operating Frequency Range 30kHz − 4MHz

q Internal Oscillator

CR, or Ceramic, or X'tal oscillation and External clock input

q STANDBY function (HALT mode)

q Wide operating voltage range 2.4V − 5.5V

q C-MOS technology

q Package outline

DIP16 / DMP16

1

16

2

15

3

14

4

13

5

12

6

11

7

10

8

9

VDD

PE1

PE0

PD1

PD0

PC0

PB0

RESET

26/Mar/2001

-1-