CDP6402 데이터 시트보기 (PDF) - Harris Semiconductor

부품명

상세내역

일치하는 목록

CDP6402 Datasheet PDF : 12 Pages

| |||

CDP6402, CDP6402C

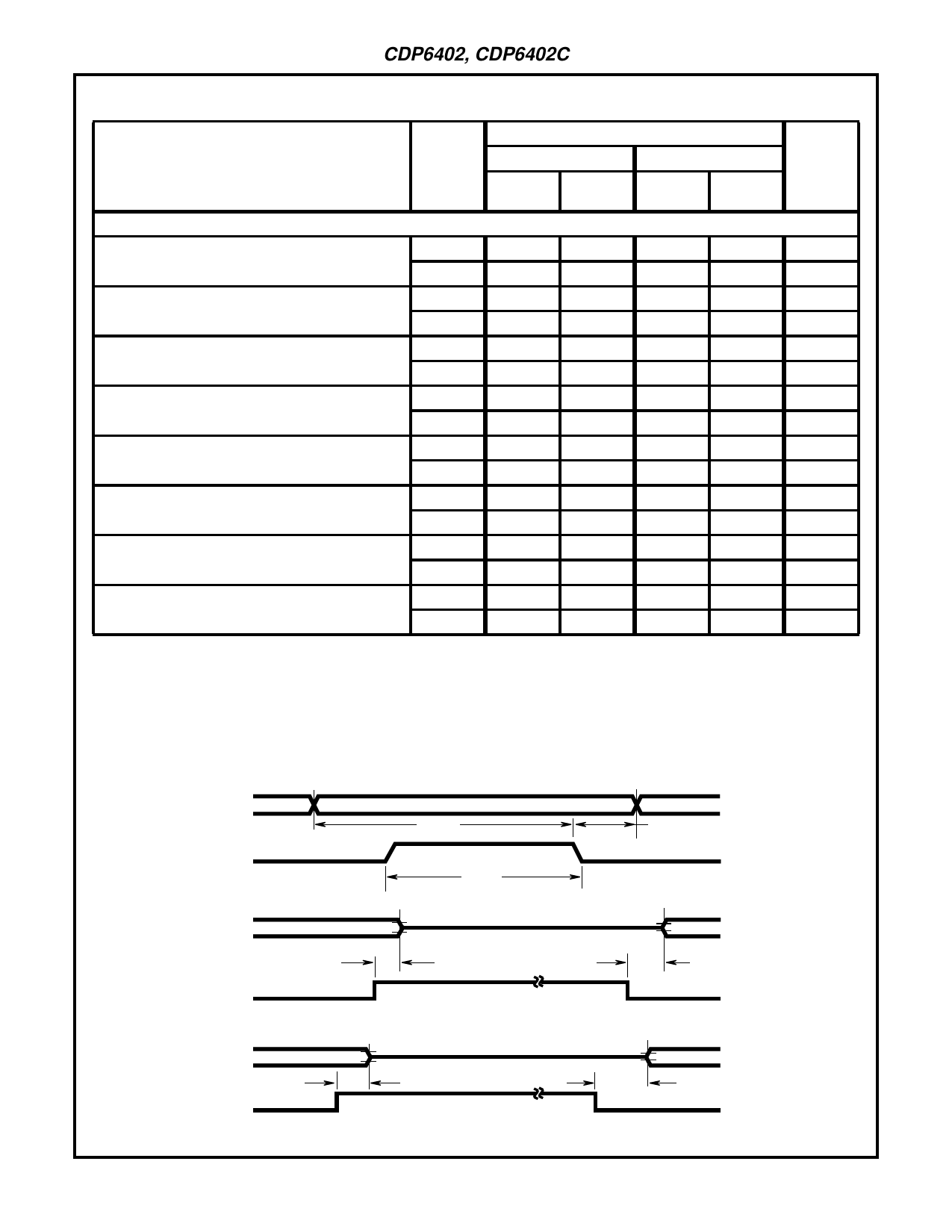

Dynamic Electrical Specifications at TA = -40oC to +85oC, VDD ±5%, tR, tF = 20ns, VIH = 0.7 VDD, VIL = 0.3 VDD, CL = 100pF

LIMITS

CDP6402

CDP6402C

(NOTE 1)

PARAMETER

VDD

(NOTE 2) (NOTE 3) (NOTE 2) (NOTE 3)

(V)

TYP

MAX

TYP

MAX

UNITS

SYSTEM TIMING (See Figure 6)

Minimum Pulse Width

CRL

tCRL

5

10

50

150

50

150

ns

40

100

-

-

ns

Minimum Setup Time

Control Word to CRL

tCWC

5

20

50

20

50

ns

10

0

40

-

-

ns

Minimum Hold Time

Control Word after CRL

tCCW

5

40

60

40

60

ns

10

20

30

-

-

ns

Propagation Delay Time

SFD High to SOD

tSFDH

5

130

200

130

200

ns

10

100

150

-

-

ns

SFD Low to SOD

tSFDL

5

130

200

130

200

ns

10

40

60

-

-

ns

RRD High to Receiver Register

High Impedance

tRRDH

5

10

80

150

80

150

ns

40

70

-

-

ns

RRD Low to Receiver Register

Active

tRRDL

5

10

80

150

80

150

ns

40

70

-

-

ns

Minimum Pulse Width

MR

5

200

400

200

400

ns

10

100

200

-

-

ns

NOTES:

1. All measurements are made at the 50% point of the transition except three-state measurements.

2. Typical values for TA = 25oC and nominal VDD.

3. Maximum limits of minimum characteristics are the values above which all devices function.

CONTROL INPUT WORD TIMING

CONTROL WORD INPUT

CONTROL WORD BYTE

tCWC

CRL

tCRL

STATUS OUTPUT TIMING

STATUS OUTPUTS

SFD

tSFDH

90%

10%

tCCW

70%

30%

tSFDL

RECEIVER REGISTER DISCONNECT TIMING

R BUS 0

90%

R BUS 7

10%

tRRDH

70%

30%

RRD

FIGURE 6. SYSTEM TIMING WAVEFORMS

tRRDL

5-82