W83195BG-118 데이터 시트보기 (PDF) - Winbond

부품명

상세내역

일치하는 목록

W83195BG-118 Datasheet PDF : 28 Pages

| |||

W83195BR-118/W83195BG-118

STEPLESS FOR INTEL 915/945 CHIPSETS

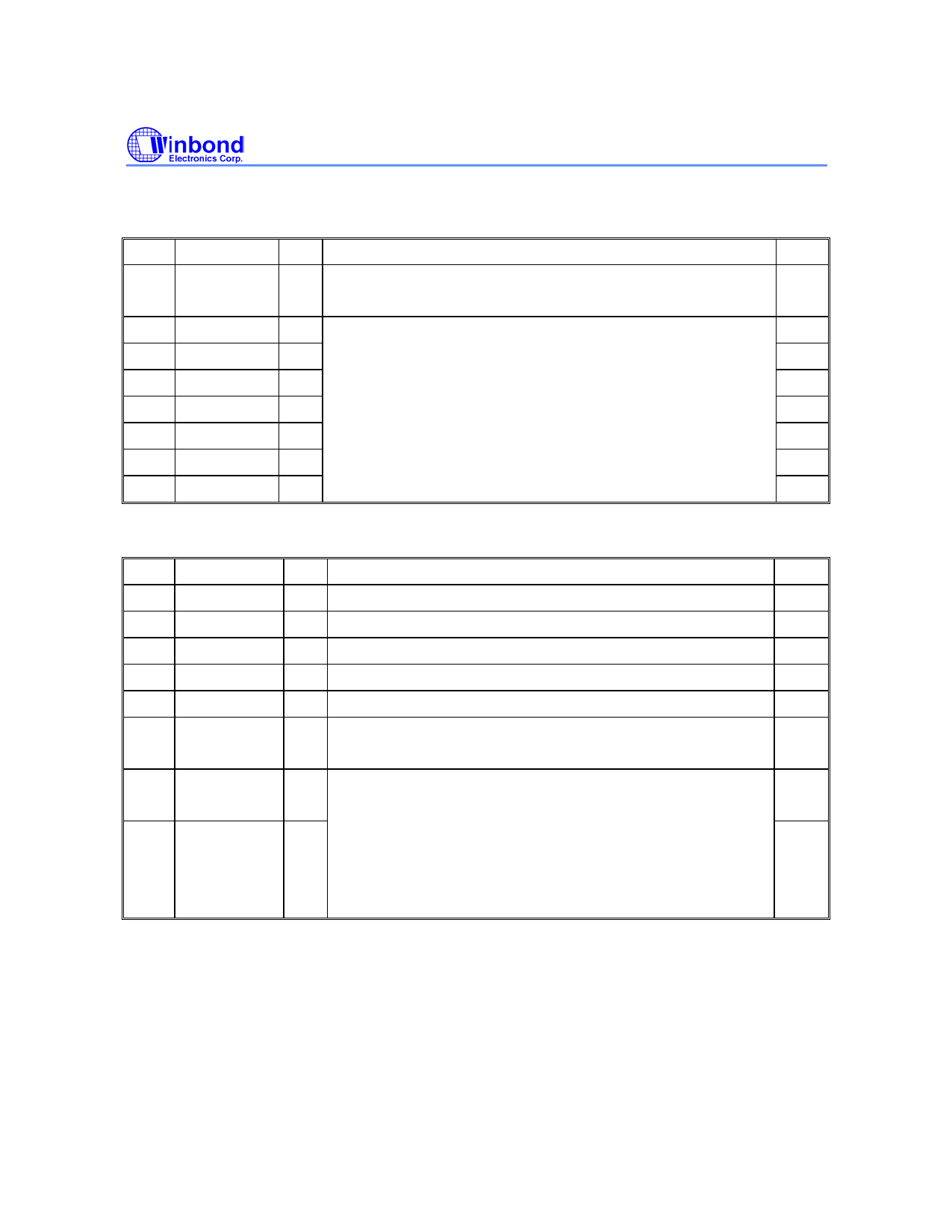

7.21 Register 20: Watch dog timer (Default: 88h)

BIT

NAME PWD

DESCRIPTION

7

Reserved 1 Reserved

TYPE

R/W

6 WD_TIME [6] 0 Setting the down count depth (Failure decision). One bit R/W

5

WD_TIME [5]

0

resolution represents 250ms. Default time depth is 8*250ms =

2.0 second. If the watchdog timer is counting, this register will

R/W

4 WD_TIME [4] 0 return present down count value.

R/W

3 WD_TIME [3] 1

R/W

2 WD_TIME [2] 0

R/W

1 WD_TIME [1] 0

R/W

0 WD_TIME [0] 0

R/W

7.22 Register 21: Asynchronous Control (Default: 4Bh)

BIT

NAME PWD

DESCRIPTION

7

Tri-state

0 Tri-state all output if set 1

6

Reserved 1 Reserved

5

Reserved 0 Reserved

4

Reserved 0 Reserved

3

Reserved 1 Reserved

2 SRC_BASE3 0 1: Asynchronous PCIE / PCI always at 100MHz / 33MHz

0: PCIE / PCI frequency are follow Bit1, 0 setting

1 FIX_ADDR<1> 1 Asynchronous PCIE / PCI frequency table selection

FIX_ADDR<1:0> =>

0 FIX_ADDR<0> 1 00: 96 / 36MHz

01 : 96 / 32MHz

10: 128 / 38.4MHz

11 : Output from PLL1

TYPE

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

- 16 -