IDT72605(2013) 데이터 시트보기 (PDF) - Integrated Device Technology

부품명

상세내역

일치하는 목록

IDT72605 Datasheet PDF : 17 Pages

| |||

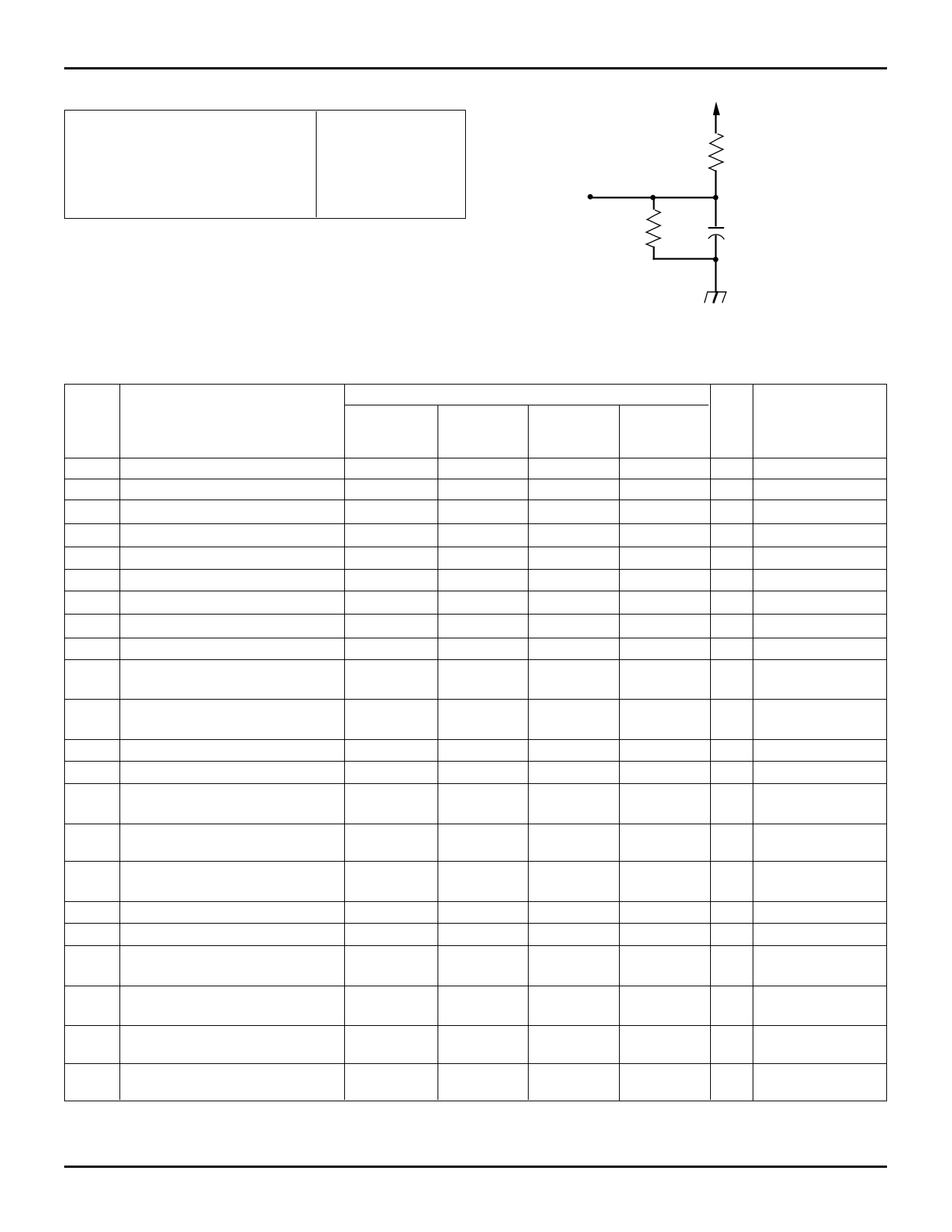

IDT72605/72615 CMOS SYNCBiFIFO™

256 x 18x 2 and 512 x 18 x 2

FUNCTIONAL DESCRIPTION

IDTs SyncBiFIFO is versatile for both multiprocessor and peripheral

applications. Data can be stored or retrieved from two sources simultaneously.

The SyncBiFIFO has registers on all inputs and outputs. Data is only

transferred into the I/O registers on clock edges, hence the interfaces are

synchronous. Two Dual-Port FIFO memory arrays are contained in the

SyncBiFIFO; one data buffer for each direction. Each port has its own

independent clock. Data transfers to the I/O registers are gated by the enable

signals. The transfer direction for each port is controlled independently by a

read/write signal. Individual output enable signals control whether the SyncBiFIFO

is driving the data lines of a port or whether those data lines are in a high-

impedance state. The processor connected to Port A of the BiFIFO can send

or receive messages directly to the Port B device using the 18-bit bypass path.

The SyncBiFIFO can be used in multiples of 18-bits. In a 36- to 36-bit

configuration, two SyncBiFIFOs operate in parallel. Both devices are pro-

grammed simultaneously, 18 data bits to each device. This configuration can

be extended to wider bus widths (54- to 54-bits, 72- to 72-bits, etc.) by adding

more SyncBiFIFOs to the configuration. Figure 1 shows multiple SyncBiFIFOs

configured for multiprocessor communication.

The microprocessor or microcontroller connected to Port A controls all

operations of the SyncBiFIFO. Thus, all Port A interface pins are inputs driven

by the controlling processor. Port B interfaces with a second processor. The

Port B control pins are inputs driven by the second processor.

RESET

Reset is accomplished whenever the Reset (RS) input is taken to a LOW state

with CSA, ENA and ENB HIGH. During reset, both internal read and write

pointers are set to the first location. A reset is required after power up before a

write operation can take place. The A→B and B→A FIFO Empty Flags (EFAB,

EFBA) and Programmable Almost-Empty flags (PAEAB, PAEBA) will be set to

LOW after tRSF. The A→B and B→A FIFO Full Flags (FFAB, FFBA) and

Programmable Almost- Full flags (PAFAB, PAFBA) will be set to HIGH after tRSF.

After the reset, the offsets of the Almost-Empty flags and Almost- Full flags for the

A→B and B→A FIFO offset default to 8.

INDUSTRIAL TEMPERATURE RANGE

PORT A INTERFACE

The SyncBiFIFO is straightforward to use in micro-processor-based

systems because each port has a standard microprocessor control set. Port A

interfaces with microprocessor through the three address pins (A2-A0) and a

Chip Select CSA pins. When CSA is asserted, A2,A1,A0 and R/WA are used

to select one of six internal resources (Table 1).

With A2=0 and A1=0, A0 determines whether data can be read out of output

register or be written into the FIFO (A0=0), or the data can pass through the

FIFO through the bypass path (A0=1).

With A2=1, four programmable flags (two A→B FIFO programmable flags

and two B→A FIFO programmable flags) can be selected: the A→B FIFO

Almost-Empty flag Offset (A1=0, A0=0), A→B FIFO Almost-Full flag Offset

(A1=0, A0=1), B→A FIFO Almost-Empty flag Offset (A1=1, A0=0), B→A FIFO

Almost-Full flag Offset (A1=1, A0=1).

Port A is disabled when CSA is deasserted and data A is in high-impedance

state.

BYPASS PATH

The bypass paths provide direct communication between Port A and Port

B. There are two full 18-bit bypass paths, one in each direction. During a bypass

operation, data is passed directly between the input and output registers, and

the FIFO memory is undisturbed.

Port A initiates and terminates all bypass operations. The bypass flag, BYPB,

is asserted to inform Port B that a bypass operation is beginning. The bypass

flag state is controlled by the Port A controls, although the BYPB signal is

synchronized to CLKB. So, BYPB is asserted on the next rising edge of CLKB

when A2A1A0=001and CSA is LOW. When Port A returns to normal FIFO mode

(A2A1A0=000 or CSA is HIGH), BYPB is deasserted on the next CLKB rising

edge.

Once the SyncBiFIFO is in bypass mode, all data transfers are controlled

by the standard Port A (R/WA, CLKA, ENA, OEA) and Port B (R/WB, CLKB,

ENB, OEB) interface pins. Each bypass path can be considered as a one word

deep FIFO. Data is held in each input register until it is read. Since the controls

CLK

MICROPROCESSOR

A

DATA

ADDR, I/0

RAM A

CONTROL

LOGIC

IDT

SYNCBIFIFO

DATA A

DATA B

CLKA

CLKB

CONTROL A CONTROL B

IDT

SYNCBIFIFO

DATA A

DATA B

CLKA

CLKB

CONTROL A CONTROL B

CONTROL

LOGIC

SYSTEM

CLOCK A

NOTES:

1. Upper SyncBiFIFO only is used in 18- to 18-bit configuration.

2. Control A consists of R/WA, ENA, OEA, CSA, A2, A1, A0. Control B consists of R/WB, ENB, OEB.

SYSTEM

CLOCK B

Figure 1. 36- to 36-bit Processor Interface Configuration

6

CLK

MICROPROCESSOR

B

DATA

ADDR, I/0

RAM B

2704 drw 05