M38504M6-201FP 데이터 시트보기 (PDF) - MITSUBISHI ELECTRIC

부품명

상세내역

일치하는 목록

M38504M6-201FP Datasheet PDF : 52 Pages

| |||

MITSUBISHI MICROCOMPUTERS

3850 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Interrupt request bit

Interrupt enable bit

Interrupt disable flag (I)

BRK instruction

Reset

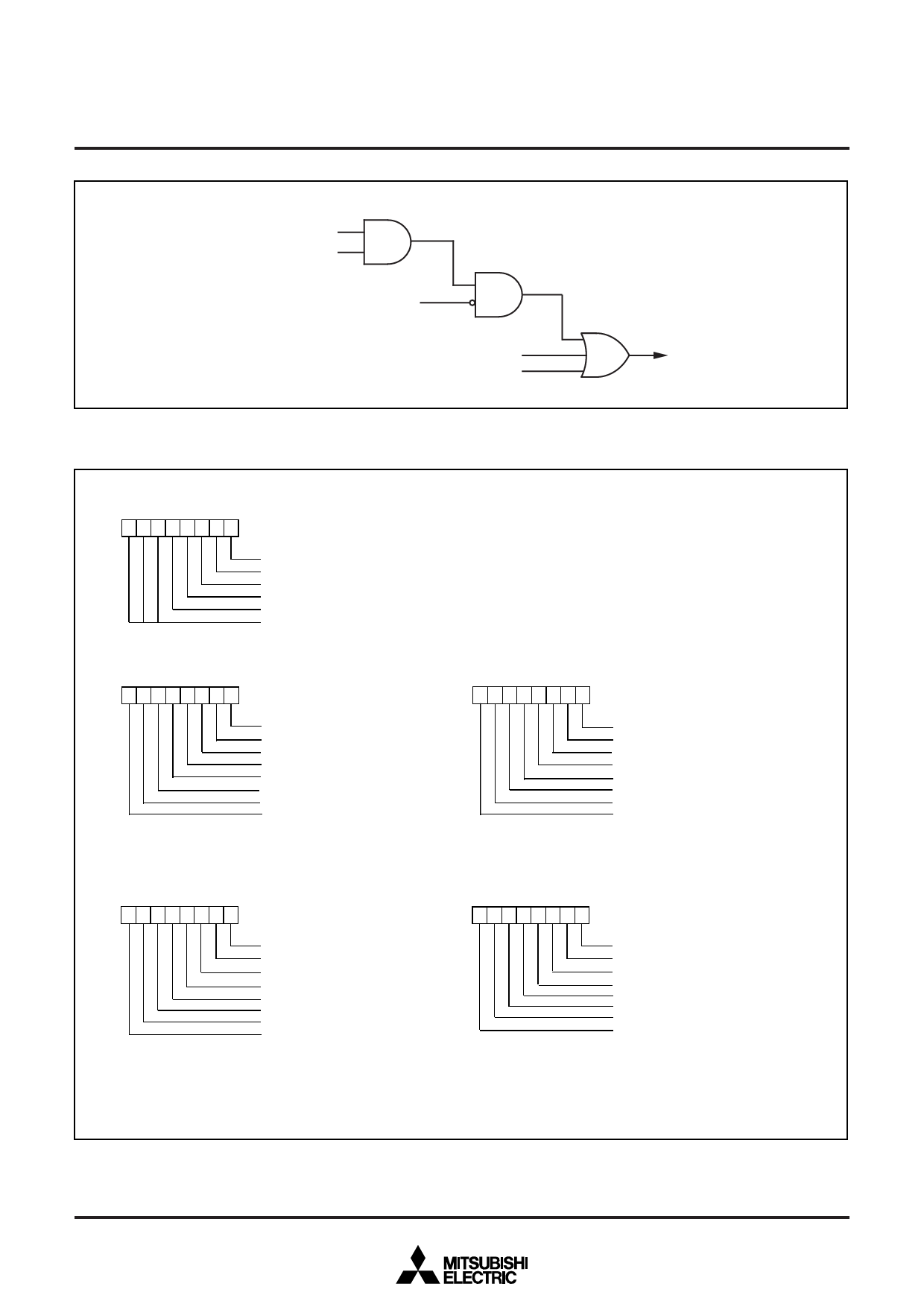

Fig. 10 Interrupt control

Interrupt request

b7

b0 Interrupt edge selection register

(INTEDGE : address 003A16)

INT0 active edge selection bit

INT1 active edge selection bit

INT2 active edge selection bit

INT3 active edge selection bit

Reserved(Do not write “1” to this bit)

Not used (returns “0” when read)

0 : Falling edge active

1 : Rising edge active

b7

b0 Interrupt request register 1

b7

b0 Interrupt request register 2

(IREQ1 : address 003C16)

(IREQ2 : address 003D16)

INT0 interrupt request bit

Reserved

INT1 interrupt request bit

INT2 interrupt request bit

INT3 interrupt request bit

Reserved

Timer X interrupt request bit

Timer Y interrupt request bit

0 : No interrupt request issued

1 : Interrupt request issued

Timer 1 interrupt request bit

Timer 2 interrupt request bit

Serial I/O reception interrupt request bit

Serial I/O transmit interrupt request bit

CNTR0 interrupt request bit

CNTR1 interrupt request bit

AD converter interrupt request bit

Not used (returns “0” when read)

0 : No interrupt request issued

1 : Interrupt request issued

b7

b0

Interrupt control register 1

(ICON1 : address 003E16)

b7

b0 Interrupt control register 2

(ICON2 : address 003F16)

INT0 interrupt enable bit

Reserved(Do not write "1" to this bit)

INT1 interrupt enable bit

INT2 interrupt enable bit

INT3 interrupt enable bit

Reserved(Do not write "1" to this bit)

Timer X interrupt enable bit

Timer Y interrupt enable bit

Timer 1 interrupt enable bit

Timer 2 interrupt enable bit

Serial I/O reception interrupt enable bit

Serial I/O transmit interrupt enable bit

CNTR0 interrupt enable bit

CNTR1 interrupt enable bit

AD converter interrupt enable bit

Not used (returns “0” when read)

(Do not write “1” to this bit)

0 : Interrupts disabled

1 : Interrupts enabled

0 : Interrupts disabled

1 : Interrupts enabled

Fig. 11 Structure of interrupt-related registers (1)

14