M37640E8FP 데이터 시트보기 (PDF) - Mitsumi

부품명

상세내역

일치하는 목록

M37640E8FP Datasheet PDF : 96 Pages

| |||

Ver 1.4

MITSUBISHI MICROCOMPUTERS

7640 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

1.15.1 Interrupt Control

Each maskable interrupt has associated with it an in-

terrupt request bit and an interrupt enable bit. These

bits, along with the I flag, determine whether interrupt

events can cause an interrupt service request to be

generated. An interrupt request bit is set to “1” when

its corresponding interrupt event is activated. The bit is

cleared to a “0” when the interrupt is serviced or when

a “0” is written to the bit. The bit can not be set high

by writing “1” to it. Each interrupt enable bit deter-

mines whether the interrupt request bit it is paired with

is seen when the interrupts are polled. When the inter-

rupt enable bit is a “0”, the interrupt request bit is not

seen; and when the enable bit is a “1”, the interrupt re-

quest is seen.

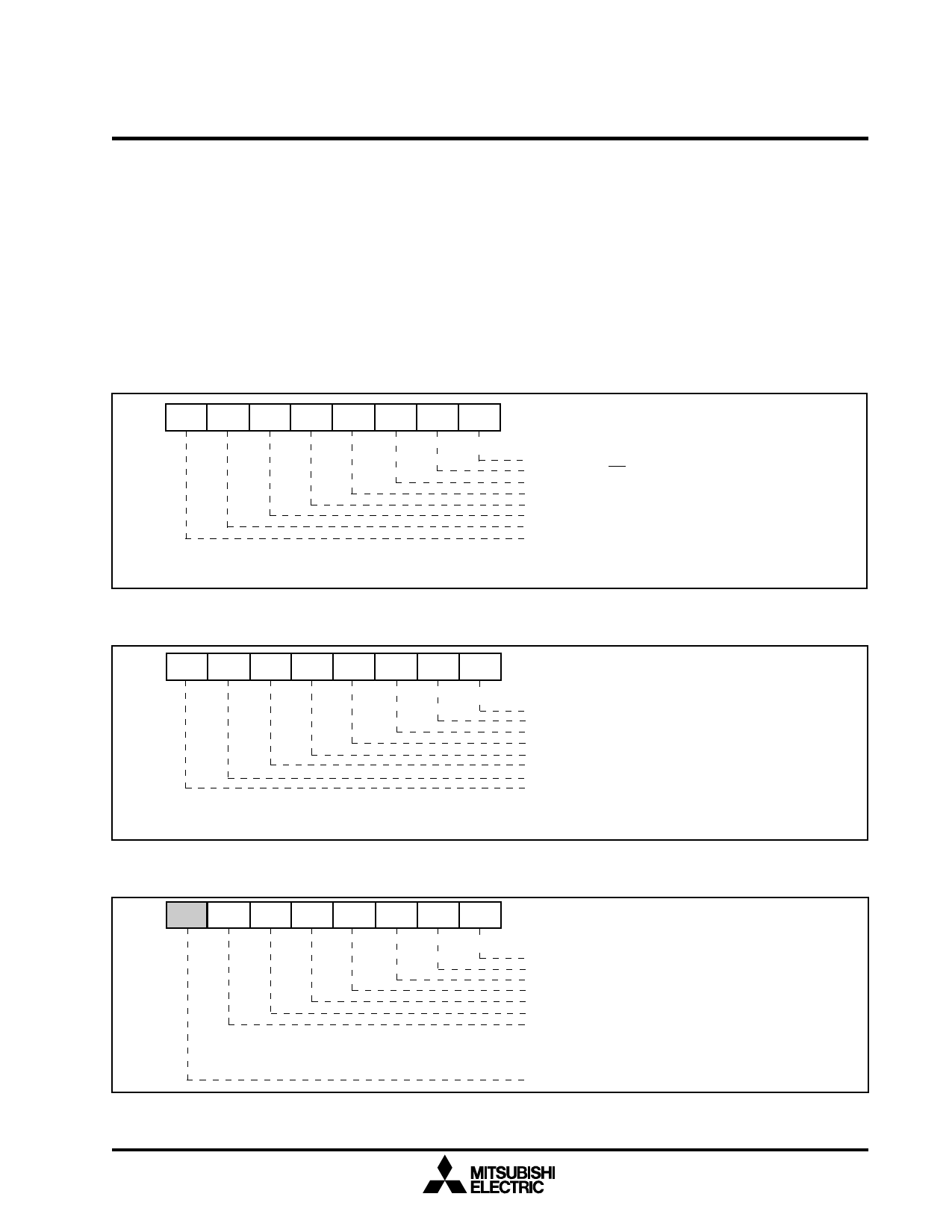

The interrupt request registers (IREQ) for the 23

maskable interrupts are shown in Figure 1.24, Figure

1.25, and Figure 1.26. The interrupt control registers

(ICON) for the 23 maskable interrupts are shown in

Figure 1.27, Figure 1.28, and Figure 1.29.

MSB

7

IRA7

IRA6

IRA5

IRA4 IRA3

IRA2

Fig. 1.24. Interrupt Request Register A (IREQA)

IRA1

IRA0

LSB Address: 000216

0

Access: R/W

Reset:

0016

IRA 0

IRA 1

IRA 2

IRA 3

IRA 4

IRA 5

IRA 6

IRA 7

USB Function Interrupt Request (bit 0)

USB SOF Interrupt Request (bit 1)

External Interrupt 0 Request (bit 2)

External Interrupt 1 Request (bit 3)

DMAC channel 0 Interrupt Request (bit 4)

DMAC channel 1 Interrupt Request (bit 5)

UART1 Receive Buffer Full Interrupt Request (bit 6)

UART1 Transmit Interrupt Request (bit 7)

0: No interrupt request issued

1: Interrupt request issued

MSB

7

IRB7

IRB6

IRB5

IRB4 IRB3

IRB2

IRB1

IRB0

LSB Address: 000316

0

Access: R/W

Reset:

0016

IRB 0

IRB 1

IRB 2

IRB 3

IRB 4

IRB 5

IRB 6

IRB 7

UART1 Error Sum Interrupt Request (bit 0)

UART2 Receive Buffer Full Interrupt Request (bit 1)

UART2 Transmit Interrupt Request (bit 2)

UART2 Error Sum Interrupt Request (bit 3)

Timer X Interrupt Request (bit 4)

Timer Y Interrupt Request (bit 5)

Timer 1 Interrupt Request (bit 6)

Timer 2 Interrupt Request (bit 7)

0: No interrupt request issued

1: Interrupt request issued

Fig. 1.25. Interrupt Request Register B (IREQB)

MSB Reserved IRC6

IRC5

IRC4 IRC3

IRC2

Fig. 1.26. Interrupt Request Register C (IREQC)

IRC1

IRC0

LSB Address: 000416

0

Access: R/W

Reset:

0016

IRC 0

IRC 1

IRC 2

IRC 3

IRC 4

IRC 5

IRC 6

Bit 7

Timer 3 Interrupt Request (bit 0)

External CNTR0 Interrupt Request (bit 1)

External CNTR1 Interrupt Request (bit 2)

SIO Interrupt Request (bit 3)

Input Buffer Full Interrupt Request (bit 4)

Output Buffer Empty Interrupt Request (bit 5)

Key-on Wake up Interrupt Request (bit 6)

0: No interrupt request issued

1: Interrupt request issued

Reserved (Read/Write “0”)

27