HYS72V4120GU-10 데이터 시트보기 (PDF) - Siemens AG

부품명

상세내역

일치하는 목록

HYS72V4120GU-10 Datasheet PDF : 11 Pages

| |||

HYS64(72)V4120GU-10

4M x 64/72 SDRAM-Module

Notes:

1. The specified values are valid when addresses are changed no more than once during tck(min.)

and when No Operation commands are registered on every rising clock edge during tRC(min).

Values are shown per module bank.

2. The specified values are valid when data inputs (DQs’ ) are stable during tRC(min.).

3. An initial pause of 100µs is required after power-up, then a Precharge All Banks command must

be given followed by 8 Auto Refresh (CBR) cycles before the Mode Register Set Operation can

begin.

4. AC timing tests have Vil = 0.4 V and Vih = 2.4 V with the timing referenced to the 1.4 V crossover

point. The transition time is measured between V ih and Vil. All AC measurements assume t T=1ns

with the AC output load circuit shown.

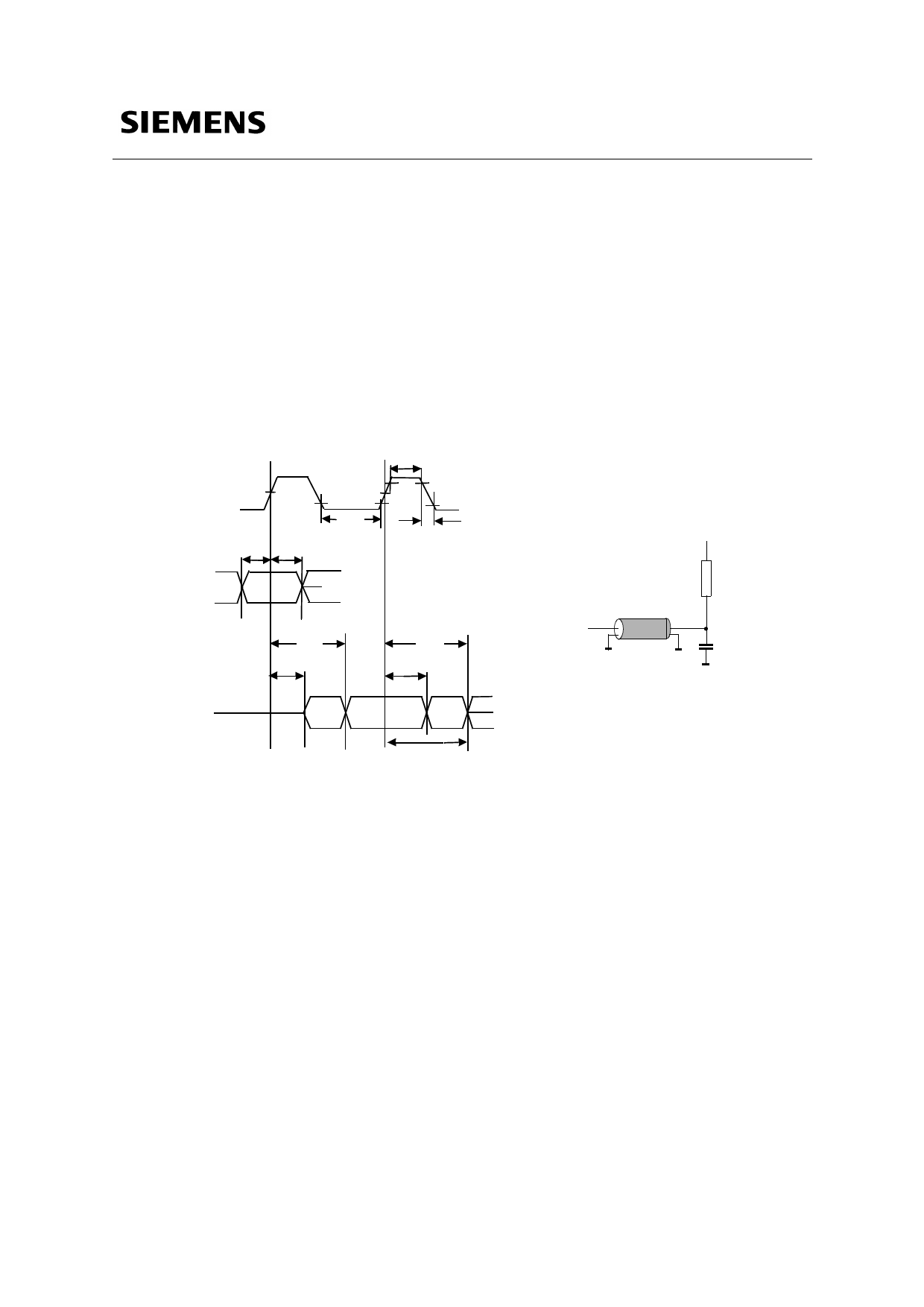

tCH

CLOCK

tCL

tSETUP tHOLD

2.4 V

0.4 V

tT

+ 1.4 V

INPUT

1.4V

tAC

tLZ

tAC

tOH

50 Ohm

Z=50 Ohm

I/O

50 pF

OUTPUT

1.4V

fig.1

tHZ

5. If clock rising time is longer than 1ns, a time (t T/2 -0.5) ns has to be added to this parameter.

6. If tT is longen than 1 ns, a time (t T -1) nshas to be added to this parameter.

7. Any time that the refresh Period has been exceeded, a minimum of two Auto (CBR) Refresh

commands must be given to “wake-up“the device.

8. Self Refresh Exit is a synchronous operation and begins on the 2nd positive clock edge after

CKE returns high. Self Refresh Exit is not complete until a time period equal to tRC is satisfied

once the Self Refresh Exit command is registered.

9. Referenced to the time which the output achieves the open circuit condition, not to output voltage

levels.

10.tDAL is equivalent to tDPL + tRP.

Semiconductor Group

9