ICSSSTUAF32869A 데이터 시트보기 (PDF) - Integrated Device Technology

부품명

상세내역

일치하는 목록

ICSSSTUAF32869A Datasheet PDF : 21 Pages

| |||

ICSSSTUAF32869A

14-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2

COMMERCIAL TEMPERATURE GRADE

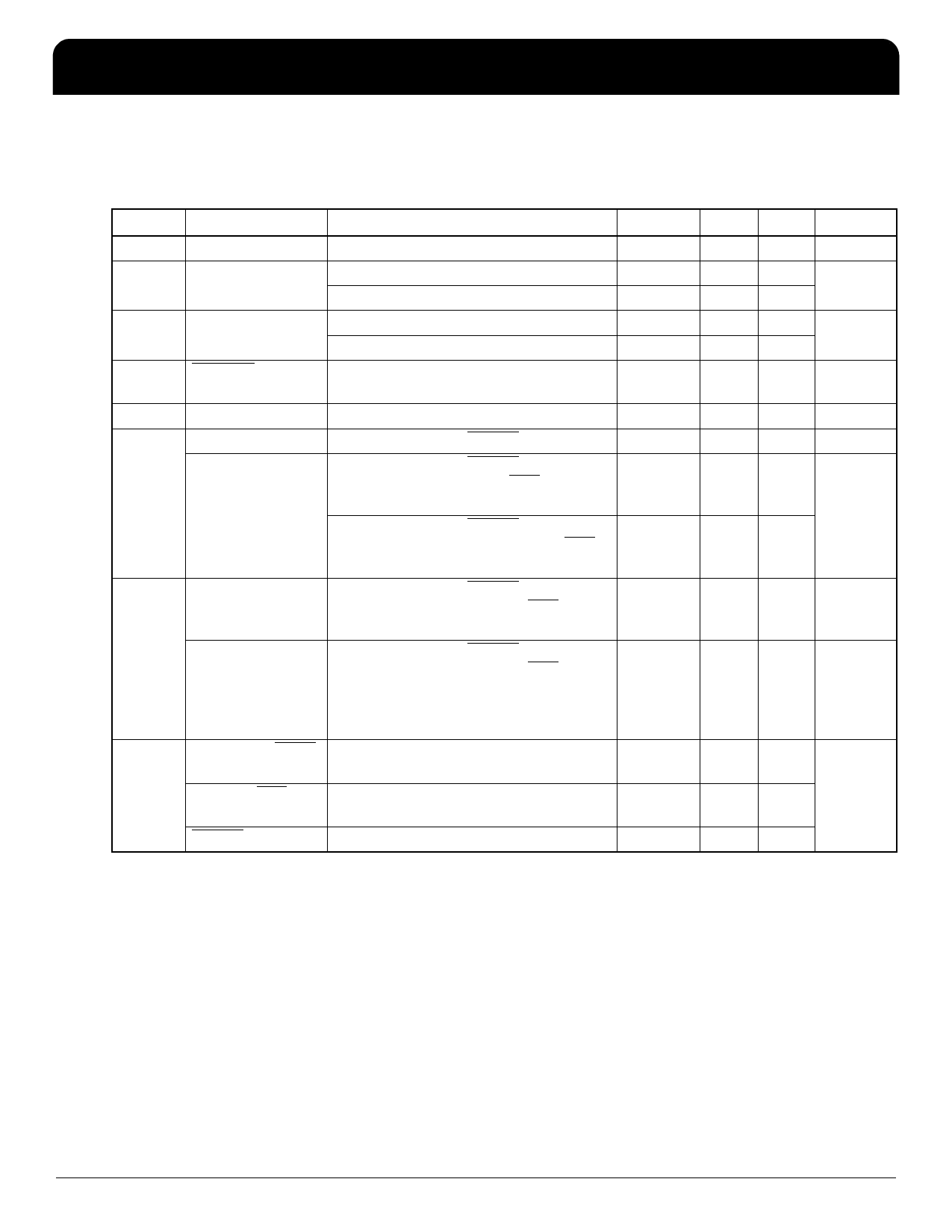

DC Electrical Characteristics Over Operating Range

Following Conditions Apply Unless Otherwise Specified:

Operating Condition: TA = 0°C to +70°C, VDDQ/VDD = 1.8V ± 0.1V.

Symbol Parameter

Test Conditions

VIK

II = -18mA

VDDQ = 1.7V, IOH = -100μA

VOH

VDDQ = 1.7V, IOH = -12mA

VDDQ = 1.7V, IOL = 100μA

VOL

VDDQ = 1.7V, IOL = 12mA

VERROL

PTYERR Output

Low Voltage

IERROL = 25mA; VDD = 1.7V

IIL All Inputs

VI = VDD or GND

Static Standby

IO = 0, VDD = 1.9V, RESET = GND

IO = 0, VDD = 1.9V, RESET = VDD, VI =

VIH(AC) or VIL(AC), CLK = CLK = VIH(AC)

IDD

or VIL(AC)

Static Operating

IO = 0, VDD = 1.9V, RESET = VDD, VI =

VIH(AC) or VIL(AC), CLK = VIH(AC), CLK =

VIL(AC)

Dynamic

Operating (clock

only)

IO = 0, VDD = 1.8V, RESET = VDD, VI =

VIH(AC) or VIL(AC), CLK and CLK

switching 50% duty cycle

IDDD

Dynamic

Operating (per

each data input)

IO = 0, VDD = 1.8V, RESET = VDD, VI =

VIH(AC) or VIL(AC), CLK and CLK

switching 50% duty cycle. One data

input switching at half clock frequency,

50% duty cycle.

Dn, PARIN, DSCn VI = VREF ± 250mV

inputs

CIN CLK and CLK

inputs

VICR = 0.9V, VIPP = 600mV

RESET

VI = VDD or GND

Min.

VDDQ-0.2

1.2

-5

2

3.5

Typ.

120

247

52

5

Max.

-1.2

0.2

0.5

0.5

+5

200

10

3

4.5

Units

V

V

V

V

μA

μA

mA

μA/Clock

MHz

μA/Clock

MHz/

Data

pF

14-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2

11

ICSSSTUAF32869A

7095/13