HEF4534B 데이터 시트보기 (PDF) - Philips Electronics

부품명

상세내역

일치하는 목록

HEF4534B Datasheet PDF : 10 Pages

| |||

Philips Semiconductors

Real time 5-decade counter

Product specification

HEF4534B

LSI

DESCRIPTION

The HEF4534B is a 5-decade ripple counter. The binary

outputs of the decade counters are time-multiplexed by an

internal scanner on four BCD outputs (O0 to O3). The

selected decade is indicated by a logic HIGH on the

appropriate digit select output (OS0: units, 1; OS1: tens,

10; OS2: hundreds, 102; OS3: thousands, 103; OS4: ten

thousands, 104).

The binary outputs (O0 to O3) and the select outputs

(OS0 to OS4) are 3-state controlled via enable inputs

EO and EOS respectively, allowing interface with other

bus orientated devices. Cascading may be accomplished

by using the carry out (TC). The counter is triggered by a

LOW to HIGH transition on the decade clock (CPA) and is

reset by a HIGH level on the master reset (MR). The

scanner is triggered by a LOW to HIGH transition on the

scanner clock (CPS) and is reset (select ten thousand

counter) by a HIGH level on the scanner reset (MRsc).

The counter can operate in four modes depending on the

state of the mode select inputs (SA, SB). The error detector

will detect an error when a positive edge on CPA is not

accompanied by a negative edge on the error detector

clock CPE or vice versa, within time limits adjusted by

external capacitors connected to Cext 1 and Cext 2. Three or

more detected errors result in a HIGH level on the error

output (OER). The error detector is reset by a HIGH level

on MR.

Schmitt-trigger action in the clock inputs makes the circuit

highly tolerant to slower clock rise and fall times.

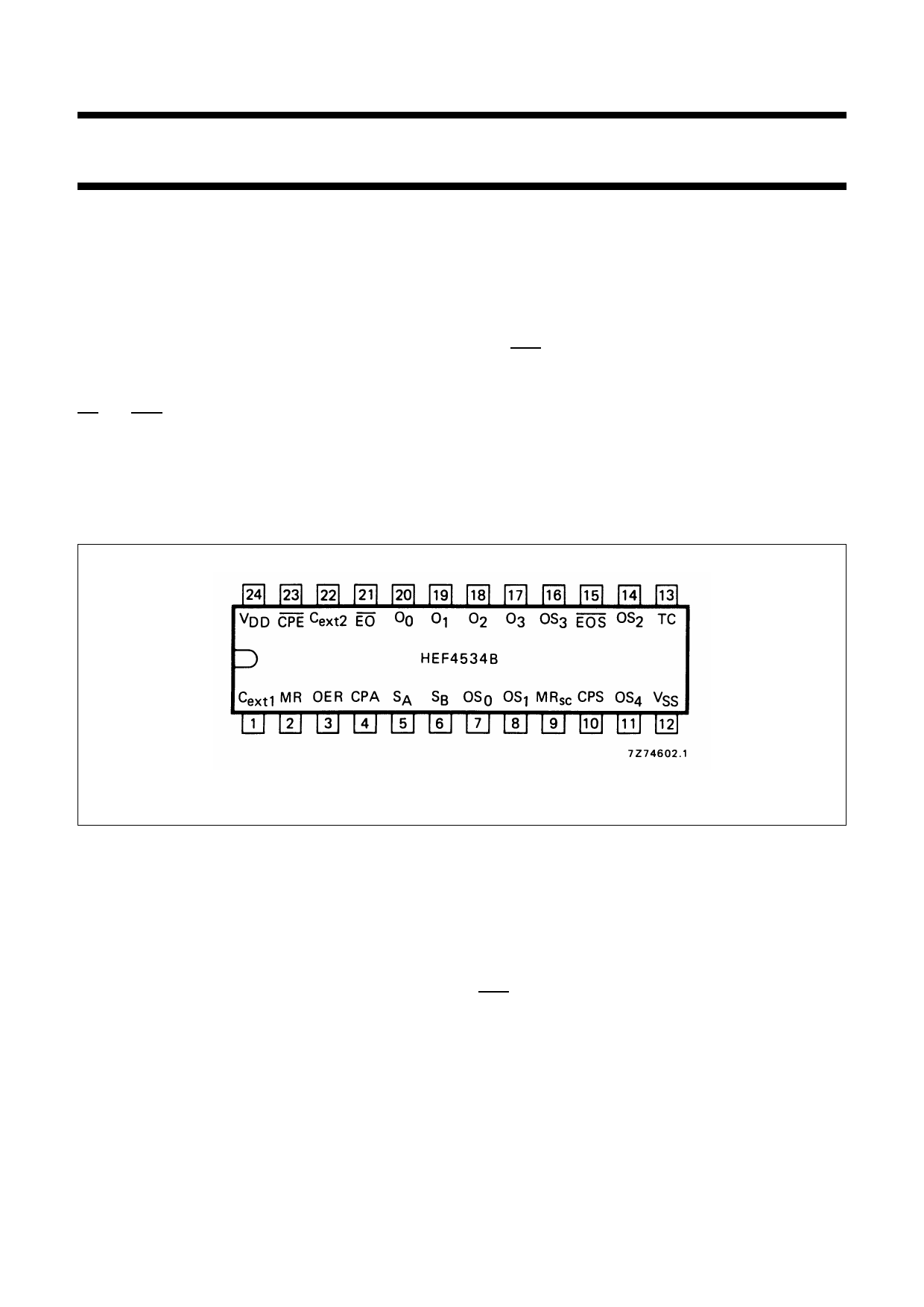

Fig.1 Pinning diagram.

PINNING

HEF4534BP(N): 24-lead DIL; plastic (SOT101-1)

HEF4534BD(F): 24-lead DIL; ceramic (cerdip) (SOT94)

HEF4534BT(D): 24-lead SO; plastic (SOT137-1)

( ): Package Designator North America

O1 to O3

OS0 to OS3

OER

CPA

CPS

CPE

SA, SB

MR

MRsc

TC

BCD outputs

digit select outputs

error output

decade clock input

scanner clock input

error detector clock input

mode select inputs

master reset input

scanner reset input

carry out

January 1995

FAMILY DATA, IDD LIMITS category LSI

See Family Specifications

2