AD6231 데이터 시트보기 (PDF) - Analog Devices

부품명

상세내역

일치하는 목록

AD6231 Datasheet PDF : 10 Pages

| |||

Preliminary Technical Data

Table 5. Truth Table Logic Levels for Transparent Gain Mode

WR

A1

A0

Gain

−VS

Low

Low

1

−VS

Low

High

10

−VS

High

Low

100

−VS

High

High

1000

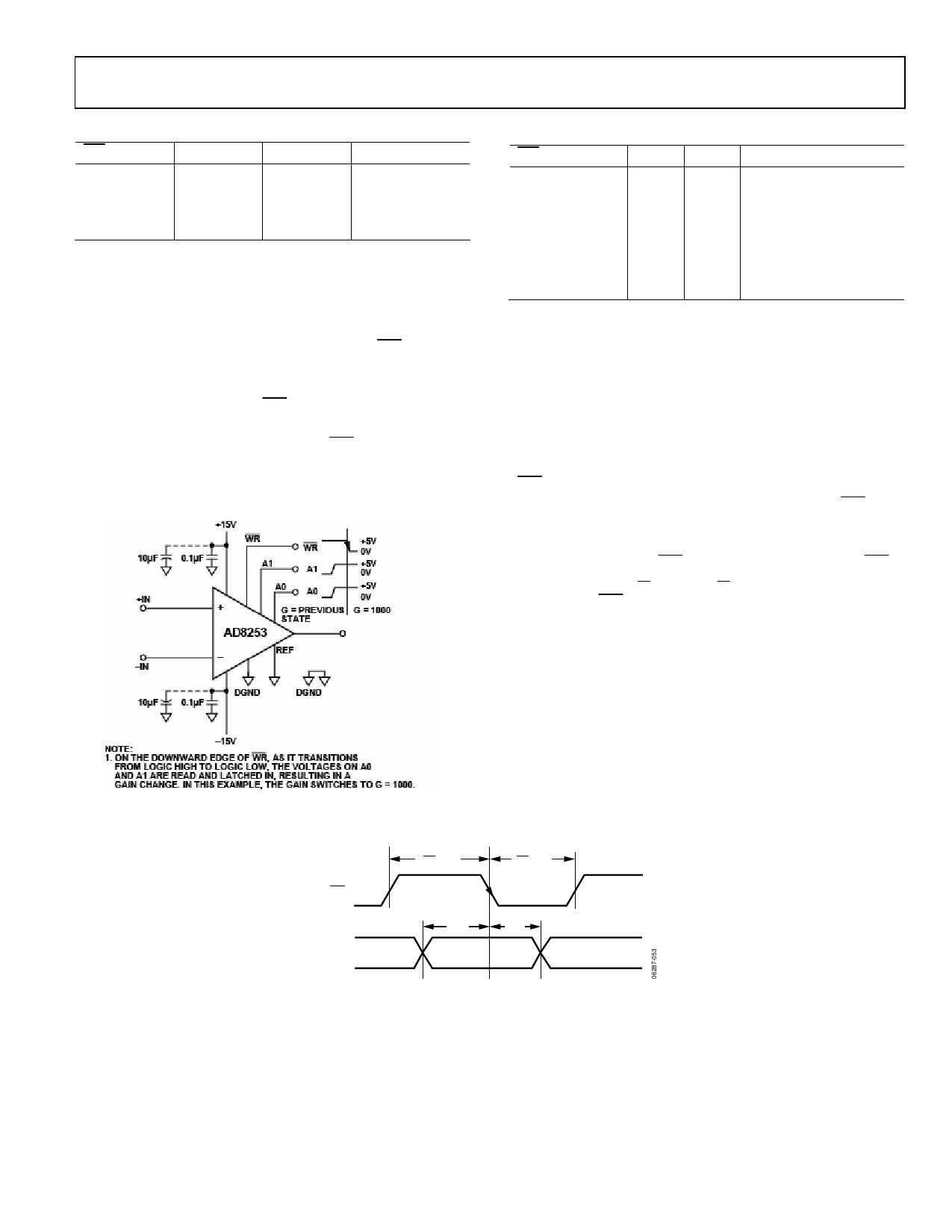

Latched Gain Mode

Some applications have multiple programmable devices such as

multiplexers or other programmable gain instrumentation

amplifiers on the same PCB. In such cases, devices can share a

data bus. The gain of the AD8253 can be set using WR as a latch,

allowing other devices to share A0 and A1. Figure 7 shows a

schematic using this method, known as latched gain mode. The

AD8253 is in this mode when WR is held at logic high or logic

low, typically 5 V and 0 V, respectively. The voltages on A0 and

A1 are read on the downward edge of the WR signal as it

transitions from logic high to logic low. This latches in the logic

levels on A0 and A1, resulting in a gain change. See the truth

table listing in Table 6 for more on these gain changes.

Figure 7. Latched Gain Mode, G = 1000

AD8253

Table 6. Truth Table Logic Levels for Latched Gain Mode

WR

A1

A0

Gain

High to Low

Low Low Change to 1

High to Low

Low High Change to 10

High to Low

High Low Change to 100

High to Low

Low to Low

Low to High

High to High

High

X1

X1

X1

High

X1

X1

X1

Change to 1000

No Change

No Change

No Change

1 X = don’t care.

Upon power-up, the AD8253 defaults to a gain of 1 when in

latched gain mode. In contrast, if the AD8253 is configured in

transparent gain mode, it starts at the gain indicated by the

voltage levels on A0 and A1 upon power-up.

Timing for Latched Gain Mode

In latched gain mode, logic levels at A0 and A1 have to be held

for a minimum setup time, tSU, before the downward edge of

WR latches in the gain. Similarly, they must be held for a

minimum hold time of tHD after the downward edge of WR to

ensure that the gain is latched in correctly. After tHD, A0 and A1

may change logic levels but the gain does not change (until the

next downward edge of WR). The minimum duration that WR

can be held high is t , WR-HIGH and t WR-LOW is the minimum

duration that WR can be held low. Digital timing specifications

are listed in Table 2. The time required for a gain change is

dominated by the settling time of the amplifier. A timing

diagram is shown in Figure 8.

When sharing a data bus with other devices, logic levels applied

to those devices can potentially feed through to the output of

the AD8253. Feedthrough can be minimized by decreasing the

edge rate of the logic signals. Furthermore, careful layout of the

PCB also reduces coupling between the digital and analog

portions of the board.

tWR-HIGH

tWR-LOW

WR

A0, A1

tSU

tHD

Figure 8. Timing Diagram for Latched Gain Mode

Rev. prA | Page 9 of 10