AD7631(2011) 데이터 시트보기 (PDF) - Analog Devices

부품명

상세내역

일치하는 목록

AD7631 Datasheet PDF : 32 Pages

| |||

AD7631

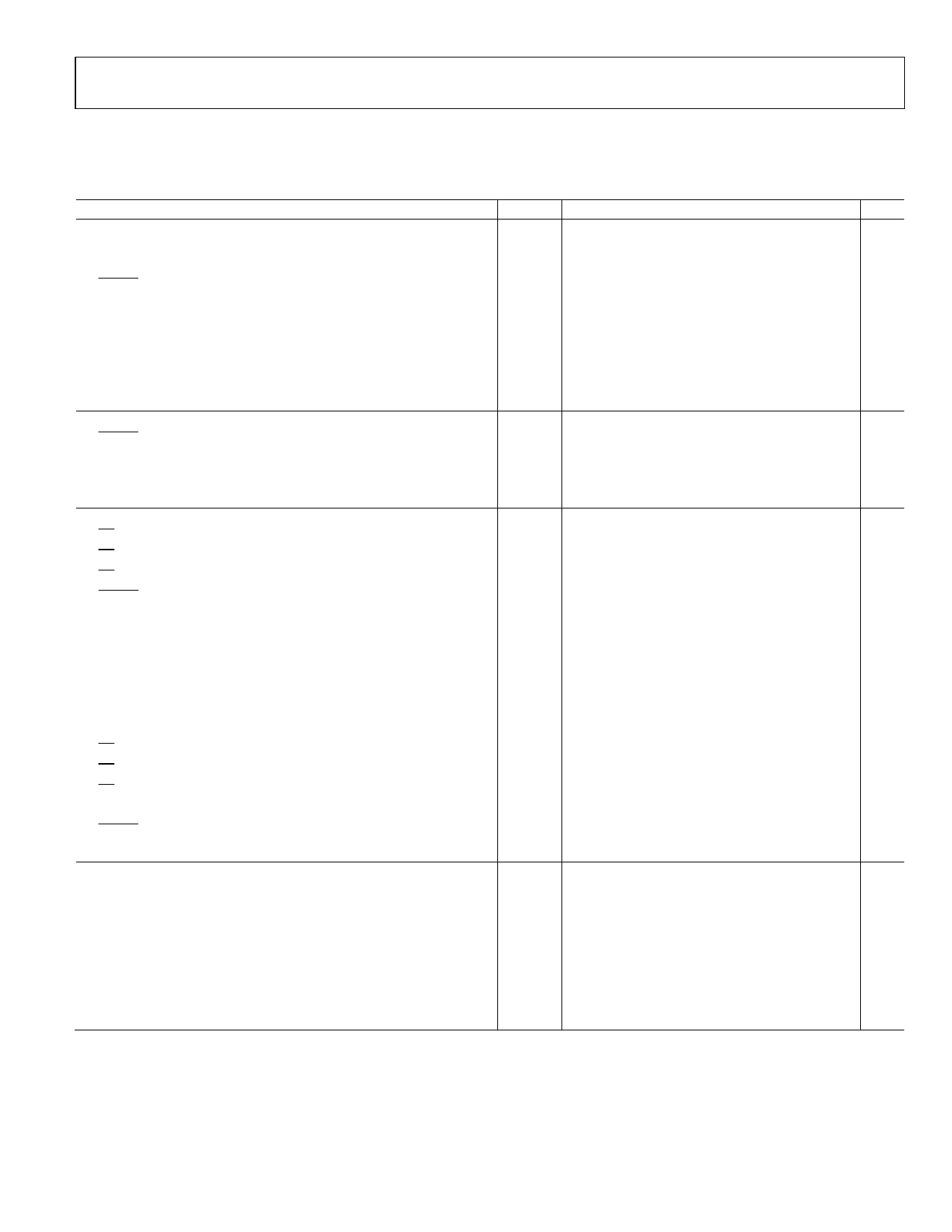

TIMING SPECIFICATIONS

AVDD = DVDD = 5 V; OVDD = 2.7 V to 5.5 V; VCC = 15 V; VEE = −15 V; VREF = 5 V; all specifications TMIN to TMAX, unless otherwise noted.

Table 3.

Parameter

Symbol Min

Typ

Max

Unit

CONVERSION AND RESET (See Figure 35 and Figure 36)

Convert Pulse Width

t1

10

ns

Time Between Conversions

t2

4.0

μs

CNVST Low to BUSY High Delay

t3

35

ns

BUSY High All Modes (Except Master Serial Read After Convert)

t4

1.68

μs

Aperture Delay

t5

2

ns

End of Conversion to BUSY Low Delay

t6

10

ns

Conversion Time

t7

1.68

μs

Acquisition Time

t8

2.32

ns

RESET Pulse Width

t9

10

ns

PARALLEL INTERFACE MODES (See Figure 37 and Figure 39)

CNVST Low to DATA Valid Delay

t10

1.65

μs

DATA Valid to BUSY Low Delay

t11

20

ns

Bus Access Request to DATA Valid

t12

40

ns

Bus Relinquish Time

t13

2

MASTER SERIAL INTERFACE MODES1 (See Figure 41 and Figure 42)

15

ns

CS Low to SYNC Valid Delay

t14

10

ns

CS Low to Internal SDCLK Valid Delay1

t15

10

ns

CS Low to SDOUT Delay

t16

10

ns

CNVST Low to SYNC Delay, Read During Convert

t17

530

ns

SYNC Asserted to SDCLK First Edge Delay

Internal SDCLK Period2

Internal SDCLK High2

Internal SDCLK Low2

SDOUT Valid Setup Time2

SDOUT Valid Hold Time2

SDCLK Last Edge to SYNC Delay2

t18

3

t19

30

t20

15

t21

10

t22

4

t23

5

t24

5

ns

45

ns

ns

ns

ns

ns

ns

CS High to SYNC HIGH-Z

t25

10

ns

CS High to Internal SDCLK HIGH-Z

t26

10

ns

CS High to SDOUT HIGH-Z

t27

10

ns

BUSY High in Master Serial Read After Convert2

t28

See Table 4

CNVST Low to SYNC Delay, Read After Convert

t29

1.5

μs

SYNC Deasserted to BUSY Low Delay

t30

25

ns

SLAVE SERIAL/SERIAL CONFIGURATION INTERFACE MODES1

(See Figure 44, Figure 45, and Figure 47)

External SDCLK, SCCLK Setup Time

t31

5

ns

External SDCLK Active Edge to SDOUT Delay

t32

2

18

ns

SDIN/SCIN Setup Time

t33

5

ns

SDIN/SCIN Hold Time

t34

5

ns

External SDCLK/SCCLK Period

t35

25

ns

External SDCLK/SCCLK High

t36

10

ns

External SDCLK/SCCLK Low

t37

10

ns

1 In serial interface modes, the SYNC, SDSCLK, and SDOUT timings are defined with a maximum load CL of 10 pF; otherwise, the load is 60 pF maximum.

2 In serial master read during convert mode. See Table 4 for serial master read after convert mode.

Rev. A | Page 5 of 32