MK50H27(1997) 데이터 시트보기 (PDF) - STMicroelectronics

부품명

상세내역

일치하는 목록

MK50H27 Datasheet PDF : 56 Pages

| |||

MK50H27

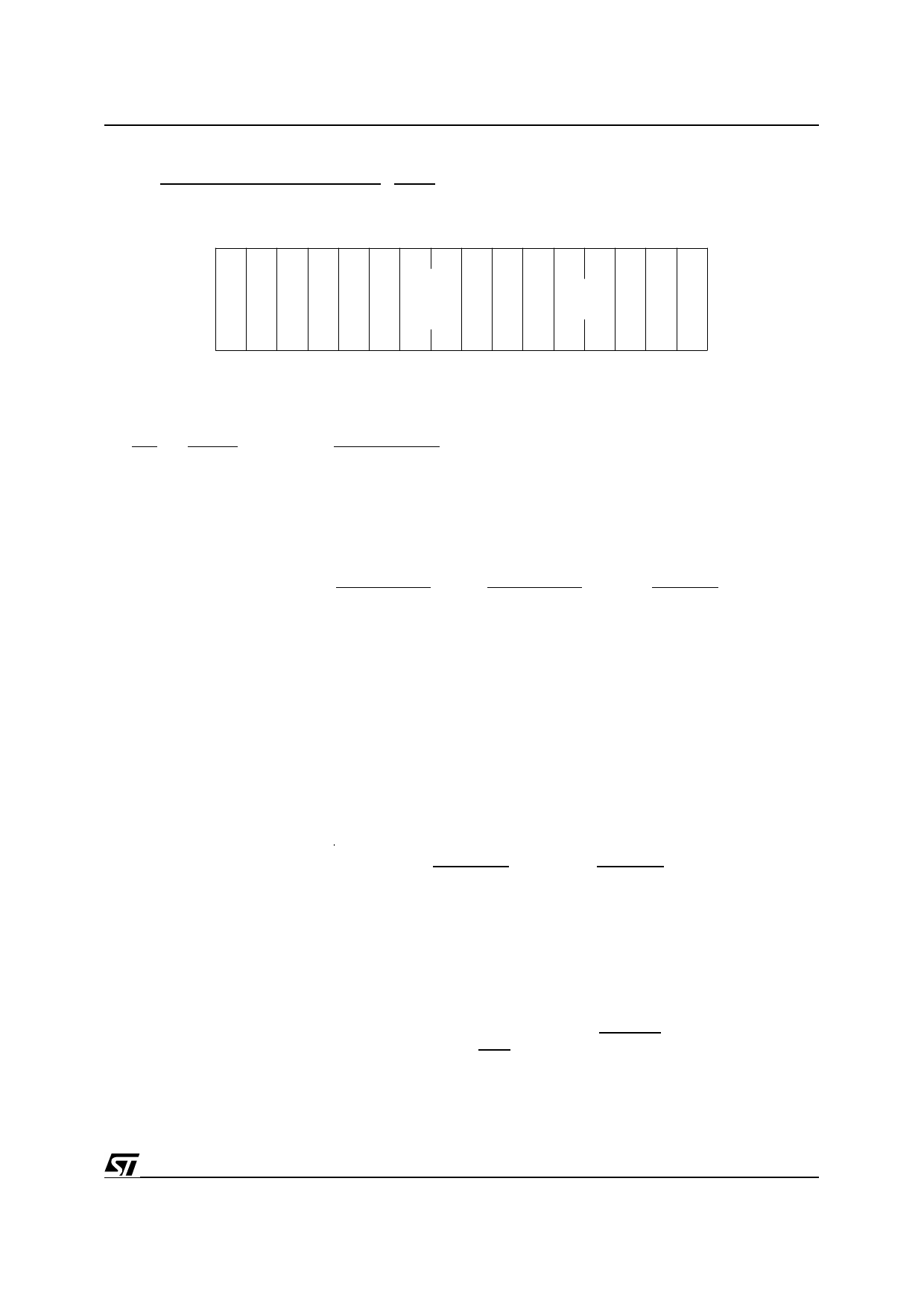

4.1.2.5 Control and Status Register 4 (CSR4)

11 1111000000 0000

54 3210987654 3210

X XR R

W WW W

D DD D 0 0

1 01 0

F

W

M

B

A

E

B

U

S

R

BB

SU

WR

PS

CT

1

:

0

B

S

W

A

C

O

P

D

N

B

C

O

N

CSR4 allows redefinition of the bus master interface.

RAP<3:1> = 4

BIT NAME

15:12 XWD0/1, RWD0/1

DESCRIPTION

These bits enable and determine the timer values for the Transmit and

Receive Watchdog Timers. These timers are independently program-

mable and are reset by any transition on the TCLK and RCLK pins re-

spectively. The Watchdog timers will expire after approximately Wn

SYSCLK cycles (if not reset by transition on TCLK / RCLK pins) and

Provider Primitive 3 or 4 will be issued. The following table shows the

selections for Wn:

XWD1/RWD1

0

0

1

1

XWD0/RWD0

0

1

0

1

Wn

Disabled

218

219

220

11:10 0

09:08 FWM

07

BAE

06

BUSR

05

BSWPC

Reserved, must be written as zero.

These bits define the FIFO watermarks. FIFO watermarks prevent

the MK50H27 from performing DMA transfers to/from the data buffers

until the FIFOs contain a minimum amount of data or space for data.

For receive data, data will only be transferred to the data buffers

after the FIFO has at least N 16-bit words or an end of signal unit

has been reached. Conversely, for transmit data, data will

only be transferred from the data buffers when the transmit FIFO

has room for at least N words of data. N is defined as follows:

FWM<1:0>

N

11

1 word

10*

9 words

01

17 words

00

25 words

* Suggested setting

Bus Address Enable: if BAE is set then the A23-A20 pins are driven

by the MK50H27 constantly providing the ability to use A23-A20 for

memory bus selection. If clear, A23-A20 behave identically to A19-

A16.

If this bit is set, pin 15 becomes input BUSREL. If this bit is clear

then pin 15 is either BM0 or BYTE depending on bit 00. For more

information see the description for pin 15 in this document. BUSR

is READ/WRITE and cleared on bus Reset.

This bit determines the byte ordering of all ”non-data” DMA transfers.

21/56