SL74HC4051D 데이터 시트보기 (PDF) - System Logic Semiconductor

부품명

상세내역

일치하는 목록

SL74HC4051D

SL74HC4051D Datasheet PDF : 9 Pages

| |||

SL74HC4051

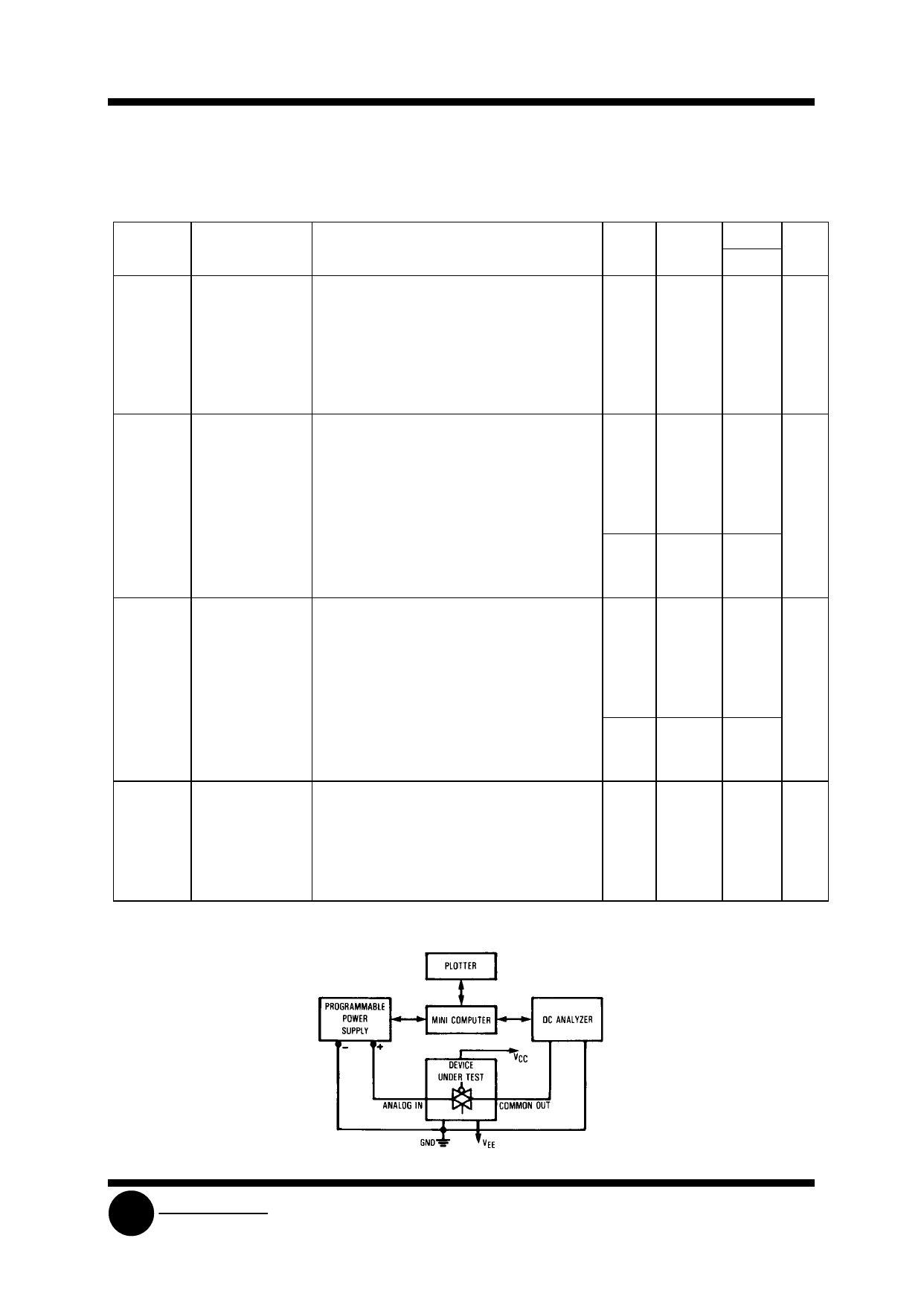

ADDITIONAL APPLICATION CHARACTERISTICS (GND = 0.0 V)

Symbol

Parameter

VCC

Test Conditions

V

BW Maximum On- fin=1 MHz Sine Wave

Channel

Adjust fin Voltage to Obtain 0 dBm at VOS

Bandwidth or Increase fin Frequence Until dB Meter

2.25

Minimum

Reads -3 dB

4.50

Frequency

RL =50 Ω, CL=10 pF

6.00

Response

(Figure 5)

-

Off-Channel

fin= Sine Wave

Feedthrough

Isolation

Adjust fin Voltage to Obtain 0 dBm at VIS

fin = 10 kHz, RL =600 Ω, CL=50 pF

(Figure 6)

2.25

4.50

6.00

fin = 1.0 MHz, RL =50 Ω, CL=10 pF

2.25

4.50

6.00

-

Feedthrough

VIN≤ 1 Mhz Square Wave (tr = tf = 6 ns)

Noise, Channel Adjust RL at Setup so that IS= 0 A Enable =

Select Input to GND

Common O/I

RL =600 Ω, CL=50 pF

2.25

(Figure 7)

4.50

6.00

RL =10 Ω, CL=10 pF

2.25

4.50

6.00

THD Total Harmonic fin= 1 kHz, RL =10 kΩ, CL=50 pF

Distortion (Figure THD = THDMeasured - THDSource

15)

VIS =4.0 VPP sine wave

2.25

VIS =8.0 VPP sine wave

4.50

VIS =11.0 VPP sine wave

6.00

VEE

V

-2.25

-4.50

-6.00

-2.25

-4.50

-6.00

-2.25

-4.50

-6.00

-2.25

-4.50

-6.00

-2.25

-4.50

-6.00

-2.25

-4.50

-6.00

Limit*

25 °C

Unit

MHz

80

80

80

dB

-50

-50

-50

-40

-40

-40

mVPP

25

105

135

35

145

190

%

0.10

0.08

0.05

* Limits not tested. Determined by design and verified by qualification.

SLS

System Logic

Semiconductor