MT8941B 데이터 시트보기 (PDF) - Mitel Networks

부품명

상세내역

일치하는 목록

MT8941B Datasheet PDF : 22 Pages

| |||

CMOS MT8941B

Crystal Clock

(12.352 MHz)

Crystal Clock

(16.384 MHz)

MT8941B

MS0

MS1

MS2

MS3

F0i

C12i

ENCV

C8Kb

C16i

ENC4o

ENC2o

VDD

CVb

C4b

C2o

F0b

VSS RST

C

R

VDD

MT8980/81

MH89760B

C1.5i

C2i

F0i

E8Ko

DSTi

DSTo

CSTi

CSTo

TxT

TxR

RxT

RxR

TRANSMIT

RECEIVE

ST-BUS

SWITCH

T1

LINK

(1.544 Mbps)

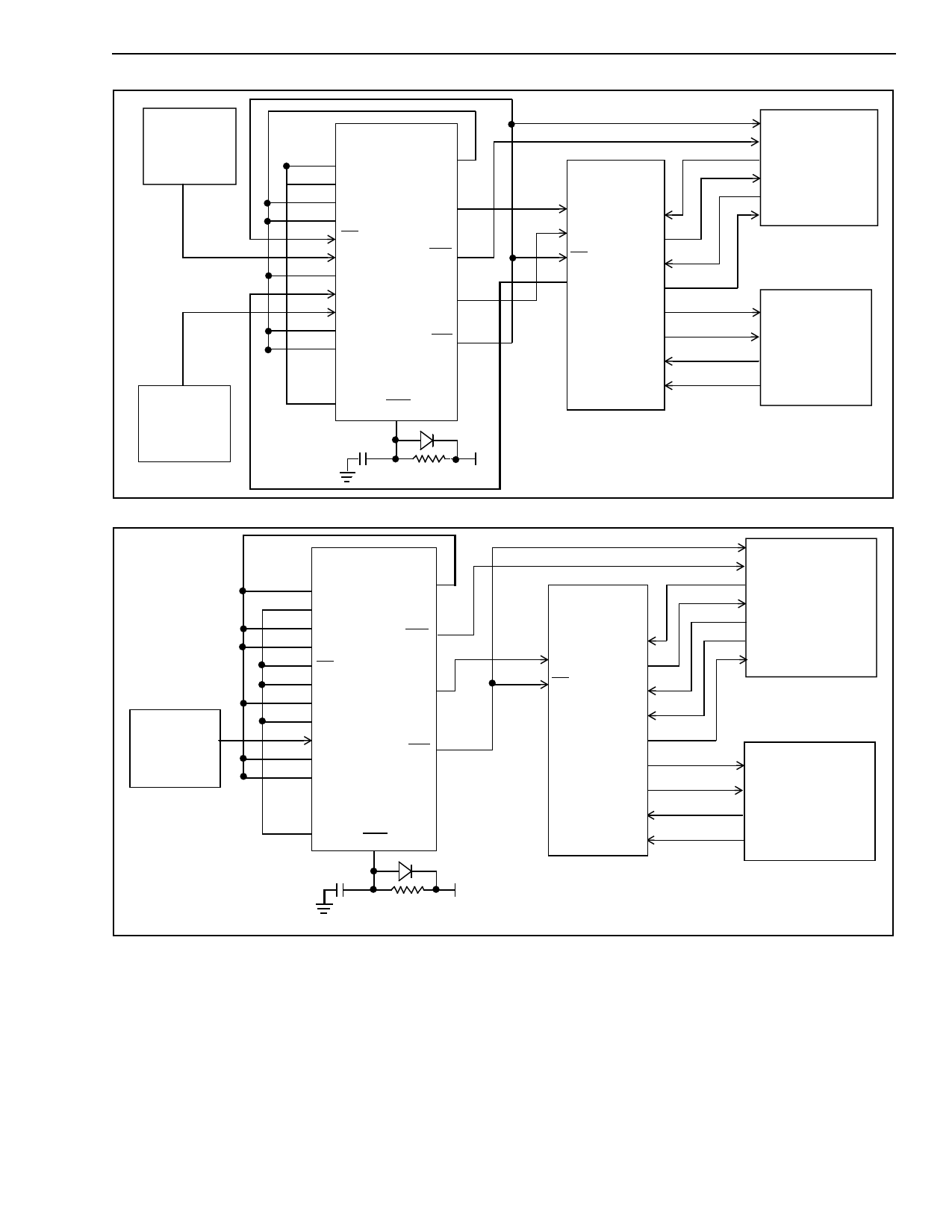

Mode of Operation for the MT8941B

DPLL #1 - NORMAL ( MS1=0)

DPLL #2 - NORMAL (MS0=0; MS1=0; MS2=1; MS3=1)

Figure 10 - Synchronization at the Slave End of the T1 Transmission Link

Crystal Clock

(16.384 MHz)

MT8941B

MS0

MS1

MS2

MS3

F0i

C12i

ENCV

C8Kb

C16i

ENC4o

ENC2o

VDD

C4b

C2o

F0b

Yo

VSS RST

MH89790B

DSTi

C2i

DSTo

F0i

CSTi0

CSTi1

CSTo

OUTA

OUTB

TRANSMIT

RxT

RECEIVE

RxR

MT8980/81

ST-BUS

SWITCH

CEPT

PRIMARY

MULTIPLEX

DIGITAL

LINK

VDD

Mode of Operation for the MT8941B

C

R

DPLL #1 - NOT USED

DPLL #2 - FREE-RUN (MS0=1; MS1=0; MS2=1; MS3=1)

Figure 11 - Synchronization at the Master End of the CEPT Digital Transmission Link

At the slave end of the link (Figure 10) both the

DPLLs are in NORMAL mode, with DPLL #2

providing the ST-BUS timing signals locked to the 8

kHz frame pulse (E8Ko) extracted from the received

signal on the T1 line. The regenerated frame pulse

is looped back to DPLL #1 to provide the T1 line

clock, which is the same as the master end.

The 12.352 MHz and 16.384 MHz crystal clock

sources are necessary for DPLL #1 and #2,

respectively.

Synchronization and Timing Signals for the

CEPT Transmission Link

The MT8941B can be used to provide the timing and

synchronization signals for the MH89790/790B,

Mitel’s CEPT (30+2) Digital Trunk Interface Hybrid.

Since the operational frequencies of the ST-BUS and

the CEPT primary multiplex digital trunk are the

same, only DPLL #2 is required.

11