MAX509ACAP 데이터 시트보기 (PDF) - Maxim Integrated

부품명

상세내역

일치하는 목록

MAX509ACAP Datasheet PDF : 20 Pages

| |||

Quad, Serial 8-Bit DACs

with Rail-to-Rail Outputs

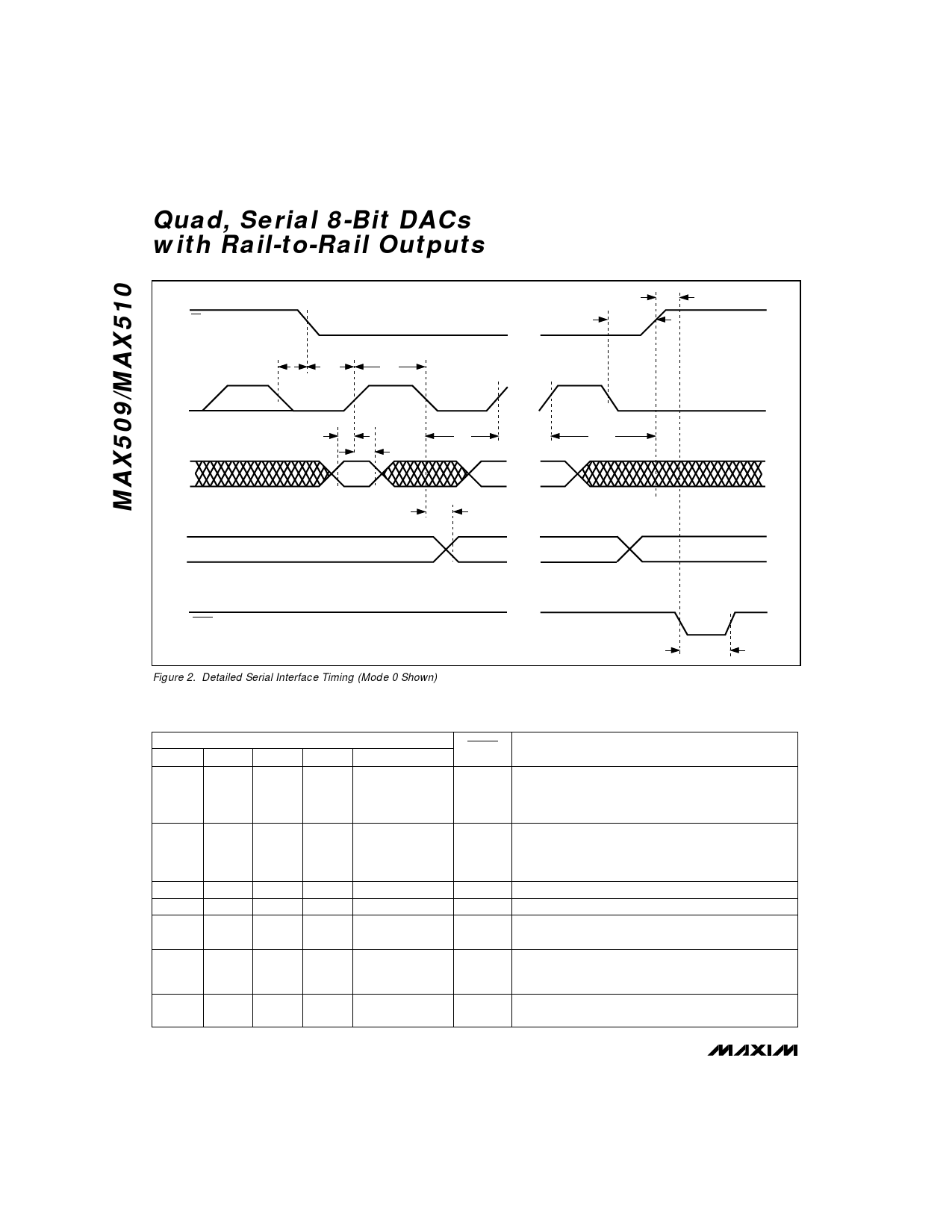

tCLL

CS

•••

tCSH2

SCLK

DIN

tCSS

tCH

tCSH0

•••

tDS

tDH

tCL

•••

tDO

tCSH1

•••

DOUT

•••

LDAC

NOTE: TIMING SPECIFICATION tCLL IS RECOMMENDED TO MINIMIZE OUTPUT GLITCH, BUT IS NOT MANDATORY.

tLDW

Figure 2. Detailed Serial Interface Timing (Mode 0 Shown)

Table 1. Serial-Interface Programming Commands

12-Bit Serial Word

LDAC

A1

A0

C1

C0 D7 . . . . . . . . D0

Function

0

0

0

1

8-Bit DAC Data

1

Load DAC A input register, DAC output unchanged.

0

1

0

1

8-Bit DAC Data

1

Load DAC B input register, DAC output unchanged.

1

0

0

1

8-Bit DAC Data

1

Load DAC C input register, DAC output unchanged.

1

1

0

1

8-Bit DAC Data

1

Load DAC D input register, DAC output unchanged.

0

0

1

1

8-Bit DAC Data

1

Load input and DAC register A.

0

1

1

1

8-Bit DAC Data

1

Load input and DAC register B.

1

0

1

1

8-Bit DAC Data

1

Load input and DAC register C.

1

1

1

1

8-Bit DAC Data

1

Load input and DAC register D.

X

0

0

0

8-Bit DAC Data

X

Update all DACs from shift register.

X

1

0

0

XXXXXXXX

X

No Operation (NOP), shifts data in shift register.

0

X

1

0

XXXXXXXX

X

“LDAC” Command, all DACs updated from respective

input registers.

Mode 1, DOUT clocked out on rising edge of SCLK

1

1

1

0

XXXXXXXX

X

(default). All DACs updated from respective input

registers.

1

0

1

0

XXXXXXXX

X

Mode 0, DOUT clocked out on falling edge of SCLK.

All DACs updated from input registers.

10 ______________________________________________________________________________________