IDT72205LB 데이터 시트보기 (PDF) - Integrated Device Technology

부품명

상세내역

일치하는 목록

IDT72205LB

IDT72205LB Datasheet PDF : 21 Pages

| |||

IDT72205LB/72215LB/72225LB/72235LB/72245LB CMOS SyncFIFO™

256 x 18, 512 x 18, 1024 x 18, 2048 x 18 and 4096 x 18

CAPACITANCE (TA = +25°C, f = 1.0MHz)

Symbol Parameter(1) Conditions

Max.

CIN(2)

Input

VIN = 0V

10

Capacitance

COUT(1,2) Output

VOUT = 0V 10

Capacitance

NOTES:

1. With output deselected, (OE = HIGH).

2. Characterized values, not currently tested.

Unit

pF

pF

2766 tbl 05

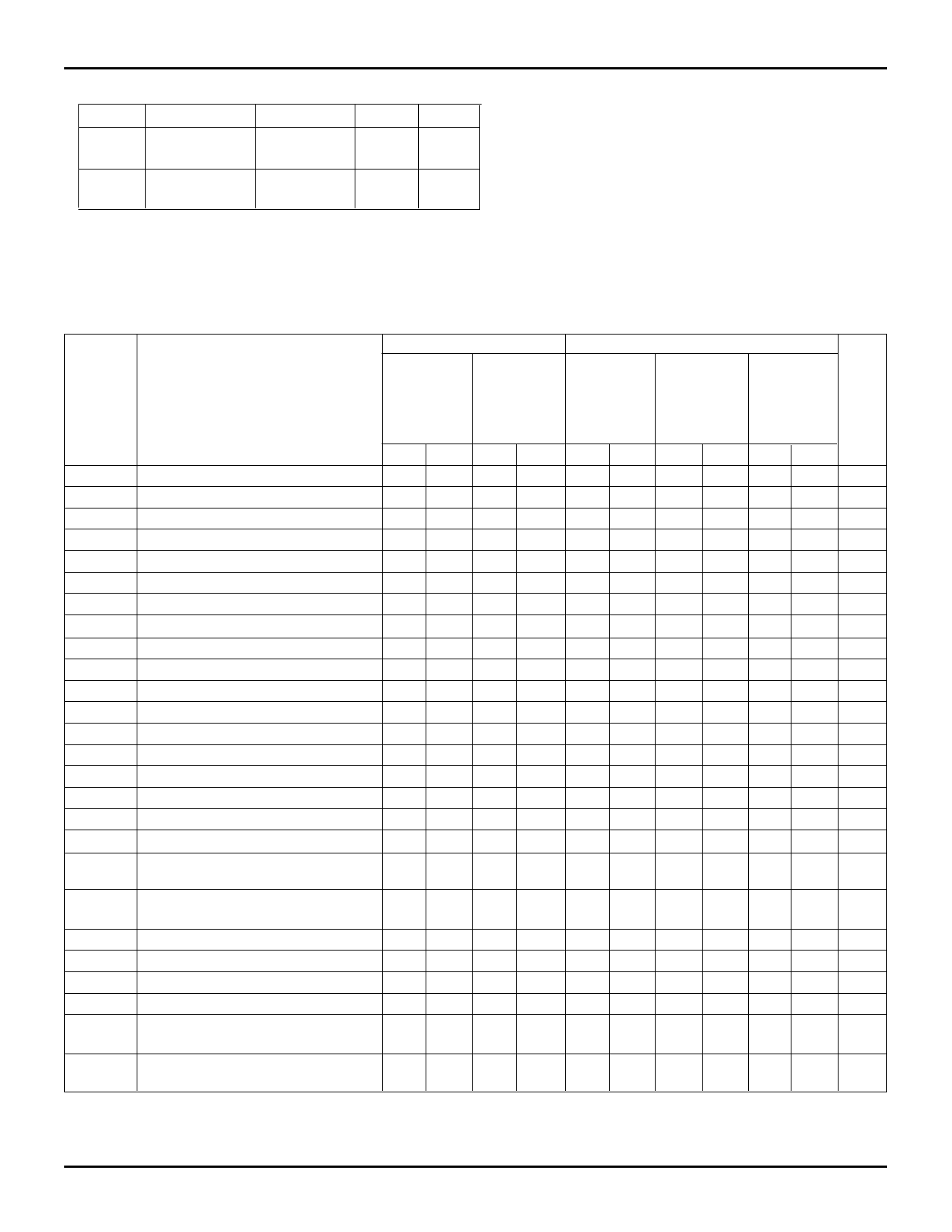

MILITARY AND COMMERCIAL TEMPERATURE RANGES

AC ELECTRICAL CHARACTERISTICS

(Commercial: VCC = 5V ± 10%, TA = 0°C to +70°C; Military: VCC = 5V ± 10%, TA = –55°C to +125°C)

Commercial

Commercial and Military

72205LB15

72215LB15

72225LB15

72235LB15

72245LB15

72205LB20

72215LB20

72225LB20

72235LB20

72245LB20

72205LB25

72215LB25

72225LB25

72235LB25

72245LB25

72205LB35

72215LB35

72225LB35

72235LB35

72245LB35

72205LB50

72215LB50

72225LB50

72235LB50

72245LB50

Symbol

Parameter

Min. Max. Min. Max. Min. Max. Min. Max. Min. Max. Unit

fS

Clock Cycle Frequency

— 66.7 — 50 — 40

— 28.6 — 20 MHz

tA

Data Access Time

2 10 2 12 3 15

3

20 3

25

ns

tCLK

Clock Cycle Time

15 — 20 — 25 —

35 — 50 —

ns

tCLKH

Clock HIGH Time

6.5 —

8

— 10 —

14 — 20 —

ns

tCLKL

Clock LOW Time

6.5 —

8

— 10 —

14 — 20 —

ns

tDS

Data Set-up Time

4—

5

—

6

—

7

— 10 —

ns

tDH

Data Hold Time

1—

1

—

1

—

2

—2—

ns

tENS

Enable Set-up Time

4—

5

—

6

—

7

— 10 —

ns

tENH

tRS

Enable Hold Time

Reset Pulse Width(1)

1—

1

—

1

—

2

—2

—

ns

15 — 20 — 25 —

35 — 50 —

ns

tRSS

Reset Set-up Time

10 — 12 — 15 —

20 — 30 —

ns

tRSR

Reset Recovery Time

10 — 12 — 15 —

20 — 30 —

ns

tRSF

Reset to Flag and Output Time

— 35 — 35 — 40

— 45 — 50

ns

tOLZ

Output Enable to Output in Low-Z(2) 0 —

0

—

0

—

0

—0

—

ns

tOE

tOHZ

Output Enable to Output Valid

—8

—

9

— 12

— 15 — 20

ns

Output Enable to Output in High-Z(2) 1

8

1

9

1 12

1

15 1

20

ns

tWFF

Write Clock to Full Flag

— 10 — 12 — 15

— 20 — 30

ns

tREF

Read Clock to Empty Flag

— 10 — 12 — 15

— 20 — 30

ns

tPAF

Clock to Programmable

Almost-Full Flag

— 28 — 30 — 35

— 40 — 40

ns

tPAE

Clock to Programmable

Almost-Empty Flag

— 28 — 30 — 35

— 40 — 40

ns

tHF

Clock to Half-Full Flag

— 28 — 30 — 35

— 40 — 40

ns

tXO

Clock to Expansion Out

— 10 — 12 — 15

— 20 — 30

ns

tXI

Expansion In Pulse Width

6.5 —

8

— 10 —

14 — 20 —

ns

tXIS

Expansion In Set-Up Time

5—

8

— 10 —

15 — 20 —

ns

tSKEW1 Skew time between Read Clock & 10 — 14 — 16 —

18 — 20 —

ns

Write Clock for Full Flag

tSKEW2 Skew time between Read Clock & 10 — 14 — 16 —

18 — 20 —

ns

Write Clock for Empty Flag

NOTES:

1. Pulse widths less than minimum values are not allowed.

2. Values guaranteed by design, not currently tested.

2766 tbl 06

5.16

6