IDT72205LB10JI8(2017) 데이터 시트보기 (PDF) - Integrated Device Technology

부품명

상세내역

일치하는 목록

IDT72205LB10JI8

(Rev.:2017)

(Rev.:2017)

IDT72205LB10JI8 Datasheet PDF : 16 Pages

| |||

IDT72205LB/72215LB/72225LB/72235LB/72245LB CMOS SyncFIFOTM

256 x 18, 512 x 18, 1,024 x 18, 2,048 x 18 and 4,096 x 18

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

SIGNAL DESCRIPTIONS:

INPUTS:

DATA IN (D0 - D17)

Data inputs for 18-bit wide data.

CONTROLS:

RESET (RS)

Reset is accomplished whenever the Reset (RS) input is taken to a LOW state.

During reset, both internal read and write pointers are set to the first location.

A reset is required after power-up before a write operation can take place. The

Full Flag (FF), Half-Full Flag (HF) and Programmable Almost-Full Flag (PAF)

will be reset to HIGH after tRSF. The Empty Flag (EF) and Programmable

Almost-Empty Flag (PAE) will be reset to LOW after tRSF. During reset, the output

register is initialized to all zeros and the offset registers are initialized to their default

values.

WRITE CLOCK (WCLK)

A write cycle is initiated on the LOW-to-HIGH transition of the Write Clock

(WCLK). Data setup and hold times must be met with respect to the LOW-to-HIGH

transition of WCLK.

The Write and Read Clocks can be asynchronous or coincident.

WRITE ENABLE (WEN)

When the WEN input is LOW and LD input is HIGH, data may be loaded into

the FIFO RAM array on the rising edge of every WCLK cycle if the device is

not full. Data is stored in the RAM array sequentially and independently of any

ongoing read operation.

When WEN is HIGH, no new data is written in the RAM array on each WCLK

cycle.

To prevent data overflow, FF will go LOW, inhibiting further write operations.

Upon the completion of a valid read cycle, FF will go HIGH allowing a write to

occur. The FF flag is updated on the rising edge of WCLK. WEN is ignored

when the FIFO is full.

OUTPUT ENABLE (OE)

When Output Enable (OE) is enabled (LOW), the parallel output buffers

receive data from the output register. When OE is disabled (HIGH), the Q output

data bus is in a high-impedance state.

LOAD (LD)

The IDT72205LB/72215LB/72225LB/72235LB/72245LB devices con-

tain two 12-bit offset registers with data on the inputs, or read on the outputs.

When the Load (LD) pin is set LOW and WEN is set LOW, data on the inputs

D0-D11 is written into the Empty Offset register on the first LOW-to-HIGH

transition of the Write Clock (WCLK). When the LD pin and (WEN) are held

LOW then data is written into the Full Offset register on the second LOW-to-HIGH

transition of (WCLK). The third transition of the write clock (WCLK) again writes

to the Empty Offset register.

However, writing all offset registers does not have to occur at one time. One

or two offset registers can be written and then by bringing the LD pin HIGH, the

FIFO is returned to normal read/write operation. When the LD pin is set LOW,

and WEN is LOW, the next offset register in sequence is written.

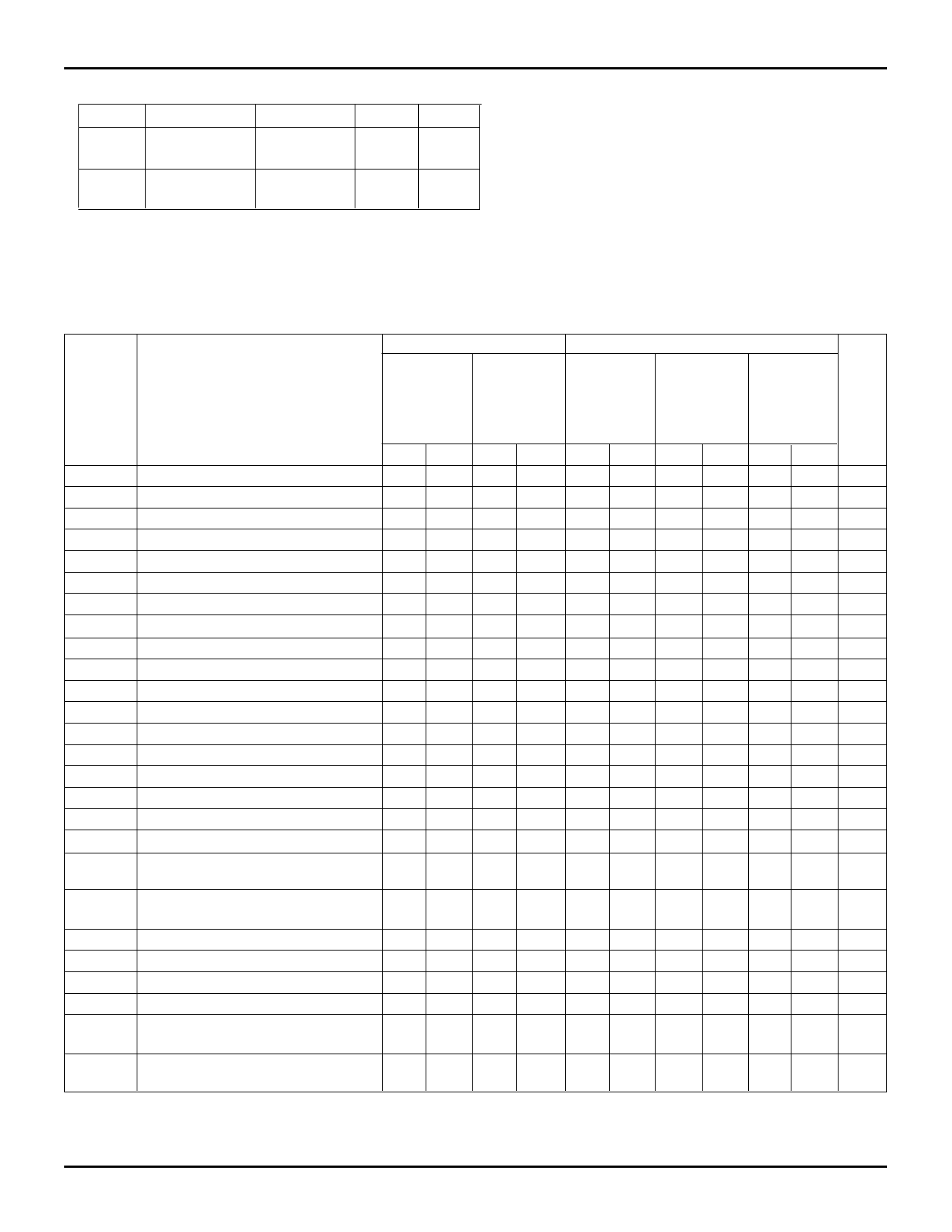

LD WEN

0

0

0

1

WCLK

Selection

Writing to offset registers:

Empty Offset

Full Offset

No Operation

1

0

Write Into FIFO

1

1

No Operation

NOTE:

1. The same selection sequence applies to reading from the registers. REN is enabled and

read is performed on the LOW-to-HIGH transition of RCLK.

Figure 2. Write Offset Register

READ CLOCK (RCLK)

Data can be read on the outputs on the LOW-to-HIGH transition of the Read

Clock (RCLK), when Output Enable (OE) is set LOW.

The Write and Read Clocks can be asynchronous or coincident.

READ ENABLE (REN)

When Read Enable is LOW and LD input is HIGH, data is loaded from the

RAM array into the output register on the rising edge of every RCLK cycle if

the device is not empty.

When the REN input is HIGH, the output register holds the previous data and

no new data is loaded into the output register. The data outputs Q0-Qn maintain

the previous data value.

Every word accessed at Qn, including the first word written to an empty

FIFO, must be requested using REN. When the last word has been read from

the FIFO, the Empty Flag (EF) will go LOW, inhibiting further read operations.

REN is ignored when the FIFO is empty. Once a write is performed, EF will

go HIGH allowing a read to occur. The EF flag is updated on the rising edge

of RCLK.

17

11

0

EMPTY OFFSET REGISTER

DEFAULT VALUE

001FH (72205) 003FH (72215):

007FH (72225/72235/72245)

17

11

0

FULL OFFSET REGISTER

DEFAULT VALUE

001FH (72205) 003FH (72215):

007FH (72225/72235/72245)

2766 drw 05

NOTE:

1. Any bits of the offset register not being programmed should be set to zero.

Figure 3. Offset Register Location and Default Values

6

MARCH 2013