IDT71321 데이터 시트보기 (PDF) - Integrated Device Technology

부품명

상세내역

일치하는 목록

IDT71321 Datasheet PDF : 13 Pages

| |||

IDT71321SA/LA AND IDT71421SA/LA

HIGH-SPEED 2K x 8 DUAL-PORT STATIC RAM WITH INTERRUPTS

COMMERCIAL TEMPERATURE RANGE

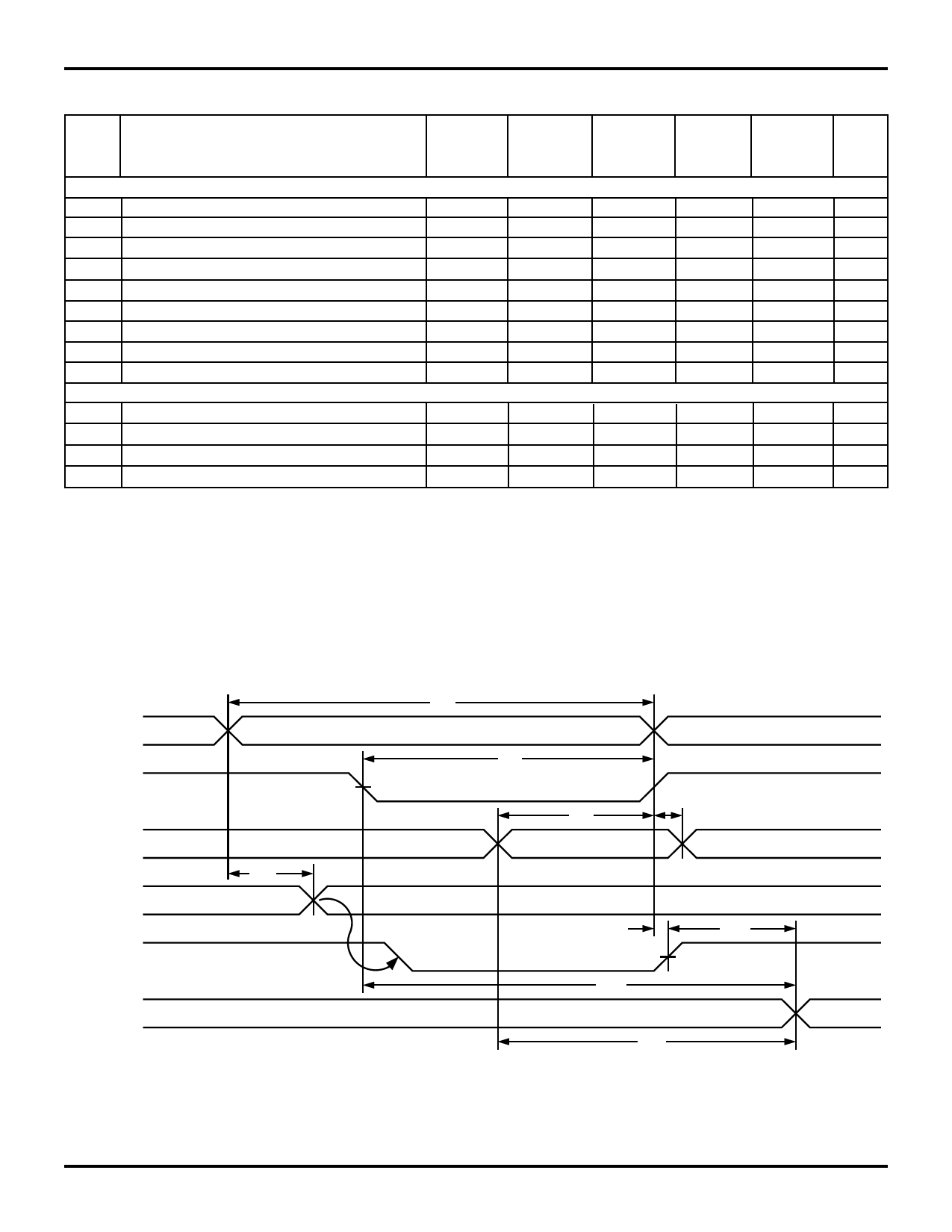

AC ELECTRICAL CHARACTERISTICS OVER THE

OPERATING TEMPERATURE AND SUPPLY VOLTAGE RANGE(6)8M824S258M824S30 7132158M824S4

71321X20 71321X25 71321X35 71321X55 71321X100

71421X25 71421X35 71421X55 71421X100

Symbol

Parameter

Min. Max. Min. Max. Min. Max. Min. Max. Min. Max. Unit

Busy Timing (For Master lDT71321 Only)

tBAA BUSY Access Time from Address

tBDA BUSY Disable Time from Address

tBAC BUSY Access Time from Chip Enable

tBDC BUSY Disable Time from Chip Enable

tWH Write Hold After BUSY(5)

tWDD Write Pulse to Data Delay(1)

tDDD Write Data Valid to Read Data Delay(1)

tAPS Arbitration Priority Set-up Time(2)

tBDD BUSY Disable to Valid Data(3)

— 20 — 20 — 20 — 30 — 50

ns

— 20 — 20 — 20 — 30 — 50

ns

— 20 — 20 — 20 — 30 — 50

ns

— 20 — 20 — 20 — 30 — 50

ns

12 — 15 — 20 — 20 — 20 —

ns

— 50 — 50 — 60 — 80 — 120 ns

— 35 — 35 — 35 — 55 — 100 ns

5—

5—

5 — 5—5 —

ns

— 25 — 35 — 35 — 50 — 65

ns

Busy Timing (For Slave IDT71421 Only)e

tWB Write to BUSY Input(4)

tWH Write Hold After BUSY(5)

tWDD Write Pulse to Data Delay(1)

tDDD Write Data Valid to Read Data Delay(1)

5— 5— 5 — 5—5

0—

0—

0 — 0—0 —

ns

12 — 15 — 20 — 20 — 20 —

ns

— 40 — 50 — 60 — 80 — 120 ns

— 30 — 35 — 35 — 55 — 100 ns

NOTES:

2689 tbl 11

1. Port-to-port delay through RAM cells from the writing port to the reading port, refer to “Timing Waveform of Write with Port-to-Port Read and BUSY."

2. To ensure that the earlier of the two ports wins.

3. tBDD is a calculated parameter and is the greater of 0, tWDD – tWP (actual), or tDDD – tDW (actual).

4. To ensure that a write cycle is inhibited on port 'B' during contention on port 'A'.

5. To ensure that a write cycle is completed on port 'B' after contention on port 'A'.

6. “X” in part numbers indicates power rating (S or L).

TIMING WAVEFORM OF WRITE WITH PORT-TO-PORT READ AND BUSY(2,3,4)

ADDR’A’

W R/ ’A’

DATAIN’A’

ADDR’B’

BUSY’B’

tAPS (1)

tWC

MATCH

tWP

tDW

VALID

MATCH

tBDA

tDH

tBDD

DATAOUT’B’

tWDD

tDDD

NOTES:

1. To ensure that the earlier of the two ports wins. tAPS is ignored for Slave (IDT71421).

2. CEL = CER = VIL.

3. OE = VIL for the reading port.

4. All timing is the same for the left and right ports. Port 'A' may be either the left or right port. Port 'B' is opposite from port 'A'.

6.03

VALID

2691 drw 10

8