AD6645(Rev0) 데이터 시트보기 (PDF) - Analog Devices

부품명

상세내역

일치하는 목록

AD6645 Datasheet PDF : 20 Pages

| |||

AD6645

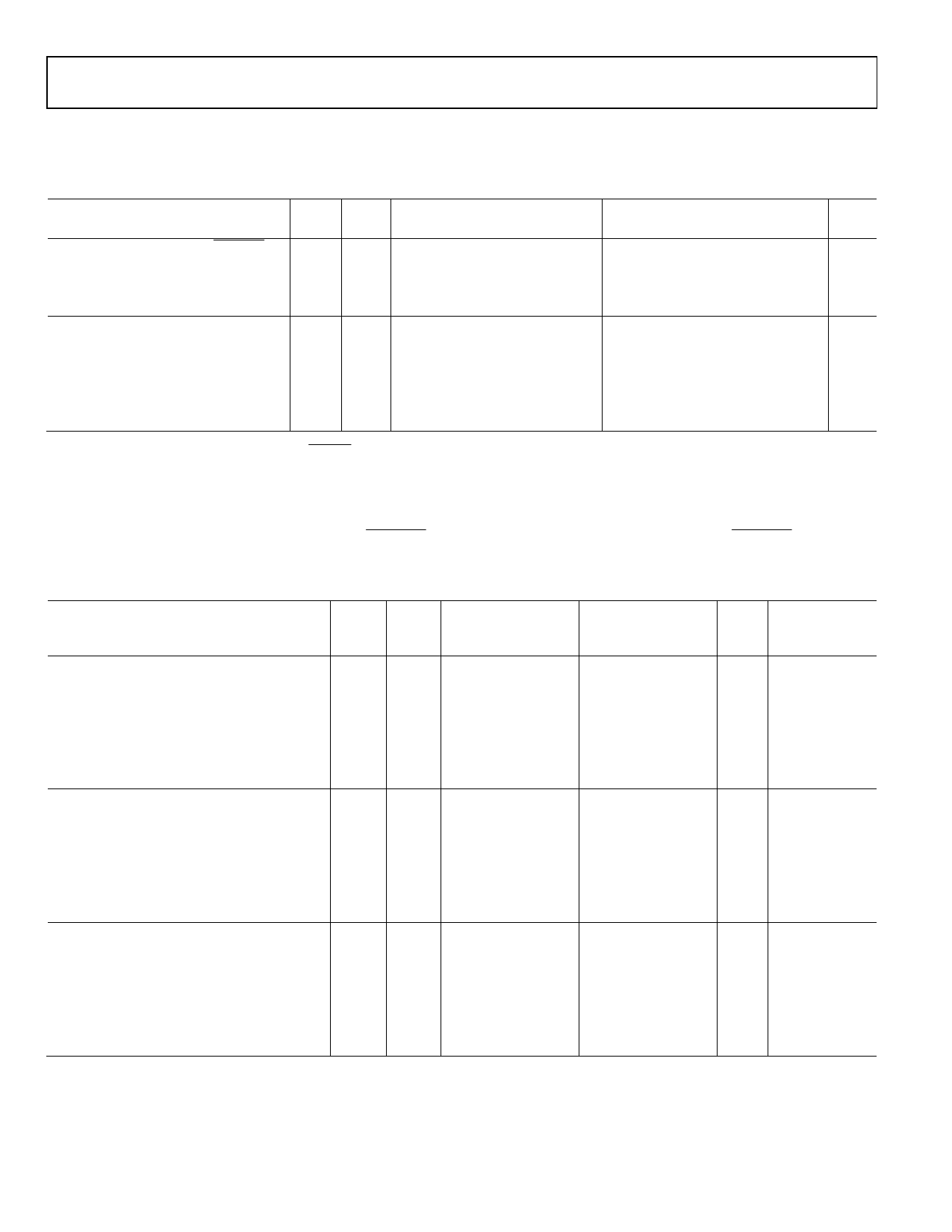

SWITCHING SPECIFICATIONS (AVCC = 5 V, DVCC = 3.3 V; ENCODE and ENCODE = 80 MSPS; TMIN = –40؇C,

(continued) TMAX = +85؇C, CLOAD = 10 pF, unless otherwise noted.)

Parameter (Conditions)

ENCODE Input Parameters1

Encode Period1 @ 80 MSPS

Encode Pulsewidth High2 @ 80 MSPS

Encode Pulsewidth Low @ 80 MSPS

ENCODE/DataReady

Encode Rising to DataReady Falling

Encode Rising to DataReady Rising

@ 80 MSPS (50% Duty Cycle)

AD6645ASQ-80

Name Temp Test Level Min

Typ

Max Unit

tENC

Full V

tENCH

Full

V

tENCL

Full

V

12.5

ns

6.25

ns

6.25

ns

tDR

Full V

tE_DR

Full

V

Full V

1.0

2.0

3.1

ns

tENCH + tDR

ns

7.3

8.3

9.4

ns

ENCODE/DATA (D13:0), OVR

ENC to DATA Falling Low

ENC to DATA Rising Low

ENCODE to DATA Delay (Hold Time)3

ENCODE to DATA Delay (Setup Time)4

Encode = 80 MSPS (50% Duty Cycle)

tE_FL

tE_RL

tH_E

tS_E

Full V

Full V

Full V

Full V

Full V

DataReady (DRY5)/DATA, OVR

DataReady to DATA Delay (Hold Time)2 tH_DR Full V

Encode = 80 MSPS (50% Duty Cycle)

DataReady to DATA Delay (Setup Time)2 tS_DR

Full V

Encode = 80 MSPS (50% Duty Cycle)

2.4

4.7

7.0

ns

1.4

3.0

4.7

ns

1.4

3.0

4.7

ns

tENC – tE_FL

ns

5.3

7.6

10.0 ns

Note 6

ns

6.6

7.2

7.9

Note 6

ns

2.1

3.6

5.1

APERTURE DELAY

APERTURE UNCERTAINTY (Jitter)

tA

25∞C V

tJ

25∞C V

–500

0.1

ps

ps rms

NOTES

1Several timing parameters are a function of tENC and tENCH.

2To compensate for a change in duty cycle for tH_DR and tS_DR use the following equation:

NewtH_DR = (tH_DR – % Change(tENCH))

NewtS_DR = (tS_DR – % Change(tENCH))

3ENCODE TO DATA Delay (Hold Time) is the absolute minimum propagation delay through the Analog-to-Digital Converter, t E_RL = tH_E.

4ENCODE TO DATA Delay (Setup Time) is calculated relative to 80 MSPS (50% duty cycle). To calculate t S_E for a given encode, use the following equation:

NewtS_E = tENC(NEW) – tENC + tS_E (i.e., for 40 MSPS: NewtS_E(TYP) = 25 ¥ 10–9 – 15.38 ¥ 10–9 + 9.8 ¥ 10–9 = 19.4 ¥ 10 –9).

5DRY is an inverted and delayed version of the encode clock. Any change in the duty cycle of the clock will correspondingly change the duty cycle of DRY.

6DataReady to DATA Delay (tH_DR and tS_DR) is calculated relative to 80 MSPS (50% duty cycle) and is dependent on t ENC and duty cycle. To calculate tH_DR and

tS_DR for a given encode, use the following equations:

NewtH_DR = tENC(NEW)/2 – tENCH + tH_DR (i.e., for 40 MSPS: NewtH_DR(TYP) = 12.5 ¥ 10–9 – 6.25 ¥ 10–9 + 7.2 ¥ 10–9 = 13.45 ¥ 10–9

NewtS_DR = tENC(NEW)/2 – tENCH + tS_DR (i.e., for 40 MSPS: NewtS_DR(TYP) = 12.5 ¥ 10–9 – 6.25 ¥ 10–9 + 3.6 ¥ 10–9 = 9.85 ¥ 10–9

Specifications subject to change without notice.

tA

N+3

N

AIN

N+1

N+2

ENC, ENC

tE_RL

D[13:0], OVR

DRY

tENC

N

tE_FL

tENCH

N+1

N–3

tENCL

N–2

N+2

tE_DR

tS_DR

N+3

tS_E

N–1

tH_DR

tDR

Figure 1. Timing Diagram

N+4

N+4

tH_E

N

–4–

REV. 0