74ALVC32PW(2014) 데이터 시트보기 (PDF) - NXP Semiconductors.

부품명

상세내역

일치하는 목록

74ALVC32PW Datasheet PDF : 14 Pages

| |||

Nexperia

74ALVC32

Quad 2-input OR gate

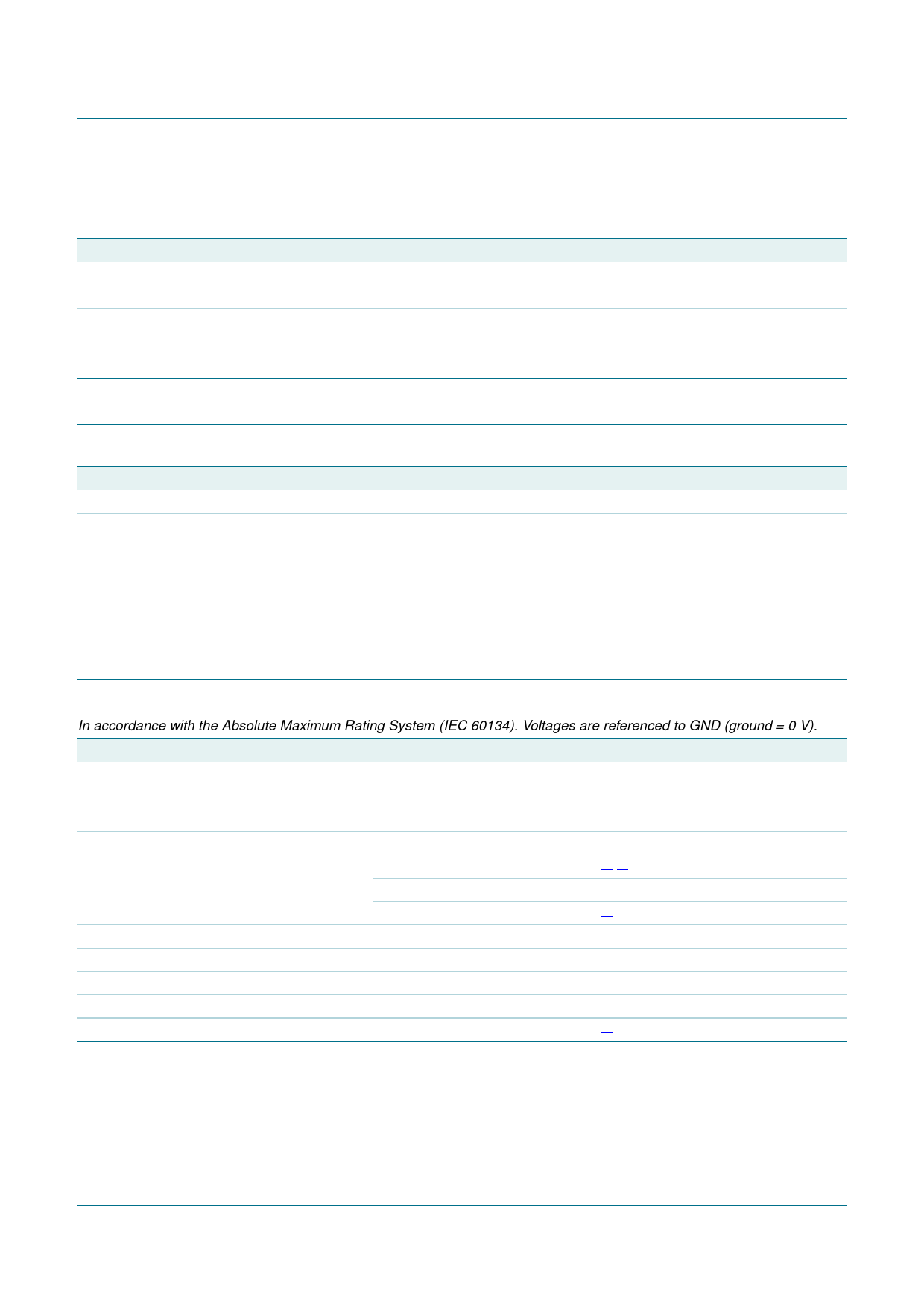

5.2 Pin description

Table 2.

Symbol

nA

nB

nY

VCC

GND

Pin description

Pin

1, 4, 9, 12

2, 5, 10, 13

3, 6, 8, 11

14

7

6. Functional description

Description

data input

data input

data output

supply voltage

ground (0 V)

Table 3. Function table[1]

Input nA

L

L

H

H

[1] H = HIGH voltage level

L = LOW voltage level

7. Limiting values

Input nB

L

H

L

H

Output nY

L

H

H

H

Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).

Symbol

Parameter

Conditions

Min

Max

Unit

VCC

supply voltage

0.5 +4.6

V

IIK

input clamping current

VI < 0 V

50

-

mA

VI

input voltage

0.5 +4.6

V

IOK

output clamping current

VO > VCC or VO < 0 V

-

50

mA

VO

output voltage

output HIGH or LOW state

[1] [2] 0.5

VCC + 0.5 V

output 3-state

0.5 +4.6

V

power-down mode, VCC = 0 V

[2] 0.5

+4.6

V

IO

output current

VO = 0 V to VCC

-

50

mA

ICC

IGND

Tstg

Ptot

supply current

ground current

storage temperature

total power dissipation

Tamb = 40 C to +85 C

-

100

mA

100 -

mA

65

+150

C

[3] -

500

mW

[1] The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

[2] When VCC = 0 V (power-down mode), the output voltage can be 3.6 V in normal operation.

[3] For SO14 packages: above 70 C derate linearly with 8 mW/K.

For TSSOP14 packages: above 60 C derate linearly with 5.5 mW/K.

For DHVQFN14 packages: above 60 C derate linearly with 4.5 mW/K.

74ALVC32

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3 — 20 January 2014

© Nexperia B.V. 2017. All rights reserved

3 of 14