MM74C32N 데이터 시트보기 (PDF) - Fairchild Semiconductor

부품명

상세내역

일치하는 목록

MM74C32N Datasheet PDF : 4 Pages

| |||

October 1987

Revised January 1999

MM74C32

Quad 2-Input OR Gate

General Description

The MM74C32 employs complementary MOS (CMOS)

transistors to achieve low power and high noise margin,

these gates provide the basic functions used in the imple-

mentation of digital integrated circuit systems. The N- and

P-channel enhancement mode transistors provide a sym-

metrical circuit with output swings essentially equal to the

supply voltage. This results in high noise immunity over a

wide supply voltage range. No DC power other than that

caused by leakage current is consumed during static con-

ditions. All inputs are protected against static discharge

damage.

Features

s Wide supply voltage range: 3.0V to 15V

s Guaranteed noise margin: 1.0V

s High noise immunity: 0.45V VCC (typ.)

s Low power TTL compatibility: fan out of 2 driving 74L

Ordering Code:

Order Number Package Number

Package Description

MM74C32M

M14A

14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150” Narrow

MM74C32N

N14A

14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide

Devices also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering code.

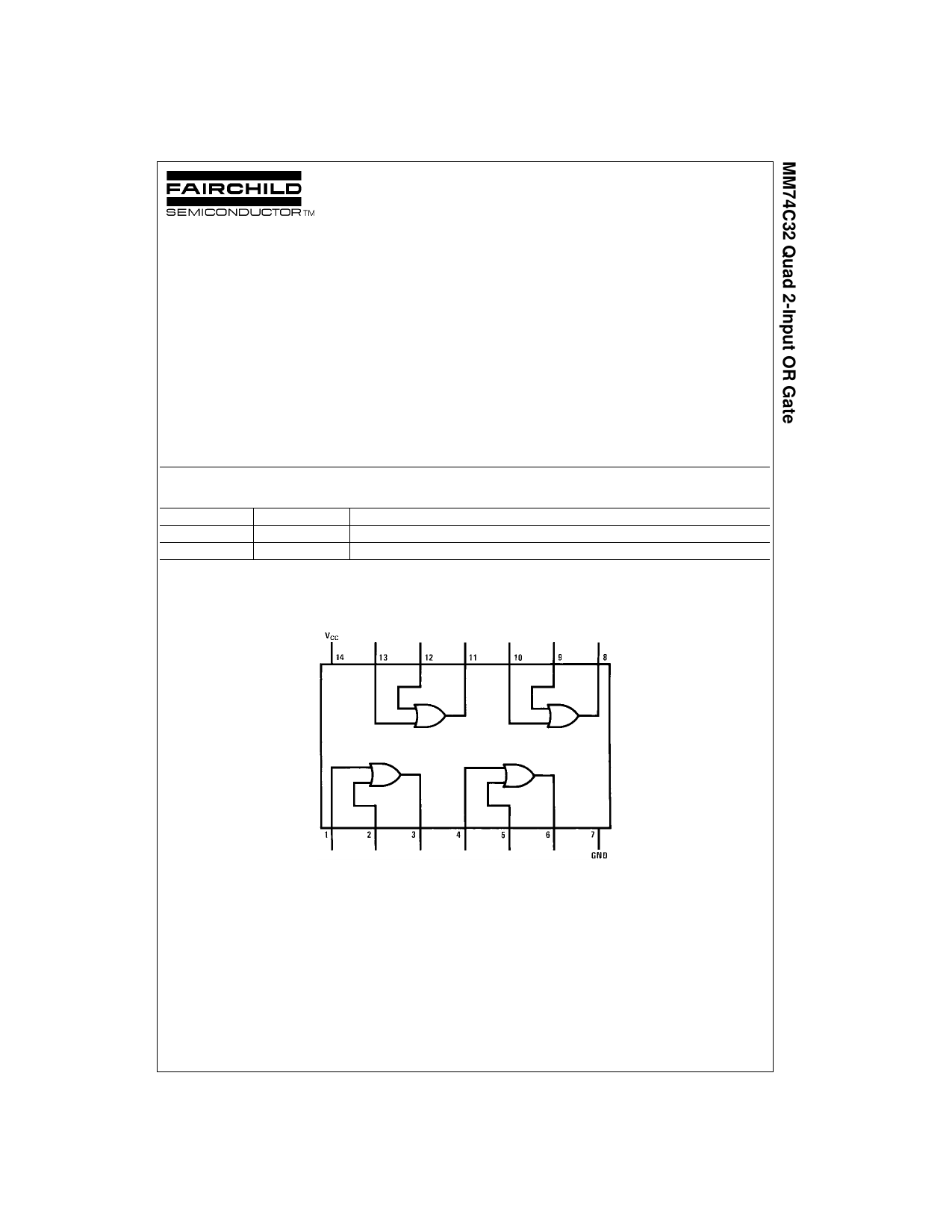

Connection Diagram

Pin Assignments for DIP and SOIC

Top View

© 1999 Fairchild Semiconductor Corporation DS005881.prf

www.fairchildsemi.com