MC54HC597 데이터 시트보기 (PDF) - Motorola => Freescale

부품명

상세내역

일치하는 목록

MC54HC597

MC54HC597 Datasheet PDF : 9 Pages

| |||

MC54/74HC597

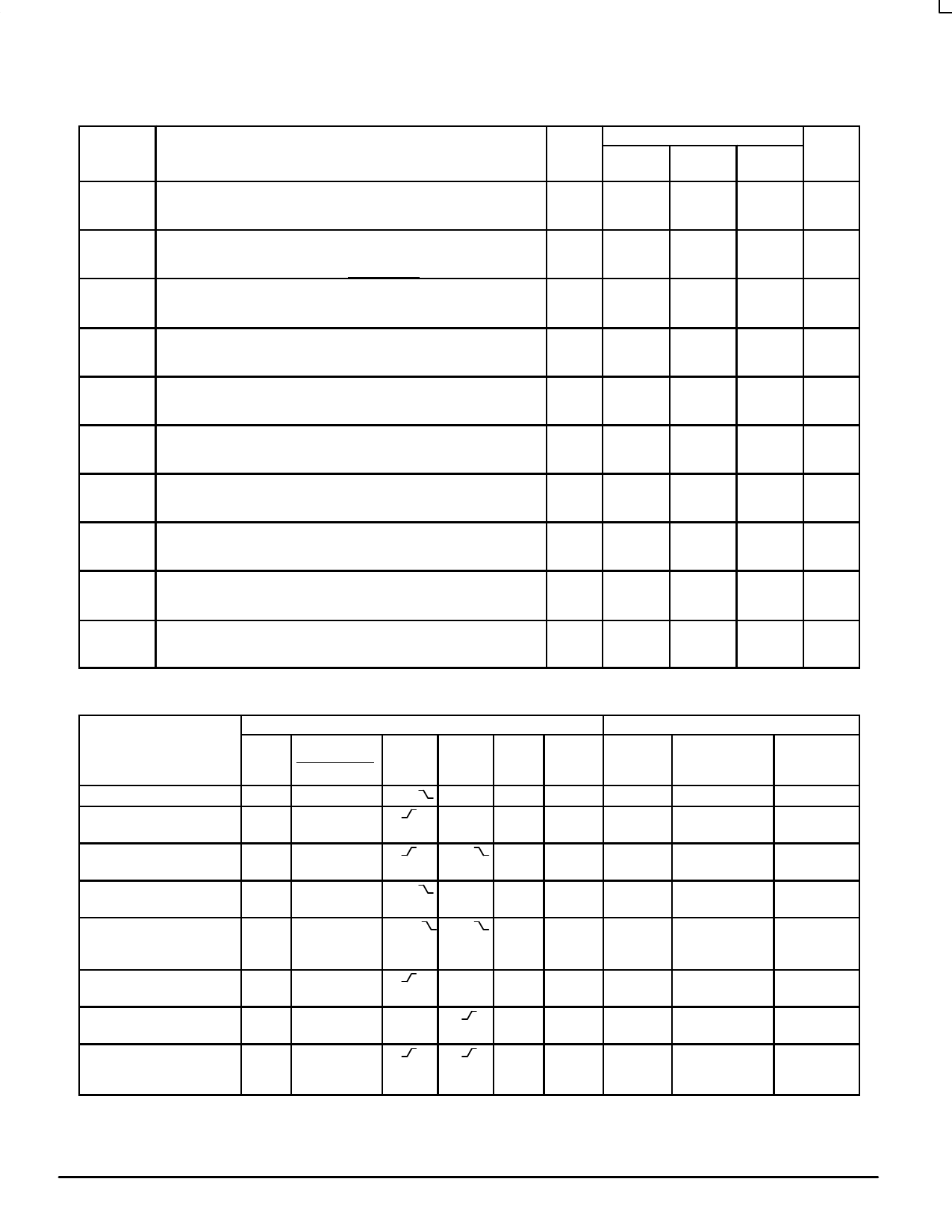

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ TIMING REQUIREMENTS (Input tr = tf = 6 ns)

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Guaranteed Limit

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Symbol

Parameter

VCC

V

v v – 55 to

25_C

85_C

125_C Unit

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tsu

Minimum Setup Time, Parallel Data inputs A–H to Latch Clock

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ (Figure 5)

2.0

100

125

150

ns

4.5

20

25

30

6.0

17

21

26

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tsu

Minimum Setup Time, Serial Data Input SA to Shift Clock

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ (Figure 6)

2.0

100

125

150

ns

4.5

20

25

30

6.0

17

21

26

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tsu

Minimum Setup Time, Serial Shift/Parallel Load to Shift Clock

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ (Figure 7)

2.0

100

125

150

ns

4.5

20

25

30

6.0

17

21

26

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ th

Minimum Hold Time, Latch Clock to Parallel Data Inputs A–H

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ (Figure 5)

2.0

25

30

40

ns

4.5

5

6

8

6.0

5

6

7

th

Minimum Hold Time, Shift Clock to Serial Data Input SA

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ (Figure 6)

2.0

5

5

5

ns

4.5

5

5

5

6.0

5

5

5

trec

Minimum Recovery Time, Reset Inactive to Shift Clock

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ (Figure 3)

2.0

100

125

150

ns

4.5

20

25

30

6.0

17

21

26

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tw

Minimum Pulse Width, Latch Clock and Shift Clock

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ (Figures 1 and 2)

2.0

80

4.5

16

6.0

14

100

120

ns

20

24

17

20

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tw

Minimum Pulse Width, Reset

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ (Figure 3)

2.0

80

4.5

16

6.0

14

100

120

ns

20

24

17

20

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tw

Minimum Pulse Width, Serial Shift/Parallel Load

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ (Figure 4)

2.0

80

4.5

16

6.0

14

100

120

ns

20

24

17

20

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tr, tf

Maximum Input Rise and Fall Times

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ (Figure 1)

2.0

1000

1000

1000

ns

4.5

500

500

500

6.0

400

400

400

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ NOTE: Information on typical parametric values can be found in Chapter 2 of the Motorola High–Speed CMOS Data Book (DL129/D).

FUNCTION TABLE

Operation

Reset shift register

Inputs

Reset

L

Serial Shift/

Parallel Load

X

Latch

Clock

L, H,

Shift

Clock

X

Serial

Input

SA

X

Parallel

Inputs

A–H

X

Resulting Function

Latch

Contents

Shift

Register

Contents

Output

QH

U

L

L

Reset shift register; load

L

X

parallel data into data latch

X

X

a–h

a–h

L

L

Load parallel data into data H

H

latch

L,H,

X

a–h

a–h

U

U

Transfer latch contents to

H

shift register

L

L, H,

X

X

X

U

LRN → SRN

LRH

Contents of data latch and H

H

L, H, L,H,

X

X

U

U

U

shift register are

unchanged

Load parallel data into data H

L

latch and shift register

X

X

a–h

a–h

a–h

h

Shift serial data into shift

H

register

Load parallel data into data H

latch and shift serial data

into shift register

LR = latch register contents

SR = shift register contents

* = depends on latch clock input

H

X

H

D

X

D

a–h

*

SRA = D;

SRG → SRH

SRN → SRN + 1

a–h

SRA = D;

SRG → SRH

SRN → SRN + 1

a–h = data at parallel data inputs A–H

D = data (L, H) at serial data input SA

U = remains unchanged

X = don’t care

MOTOROLA

4

High–Speed CMOS Logic Data

DL129 — Rev 6