UT62256CSC-35LL 데이터 시트보기 (PDF) - Utron Technology Inc

부품명

상세내역

일치하는 목록

UT62256CSC-35LL Datasheet PDF : 12 Pages

| |||

Rev. 1.3

UTRON

UT62256C

32K X 8 BIT LOW POWER CMOS SRAM

Notes :

1. WE , CE must be high during all address transitions.

2.A write occurs during the overlap of a low CE , low WE .

3. During a WE controlled write cycle with OE low, tWP must be greater than tWHZ+tDW to allow the drivers to turn off and data to be placed

on the bus.

4.During this period, I/O pins are in the output state, and input signals must not be applied.

5. If the CE low transition occurs simultaneously with or after WE low transition, the outputs remain in a high impedance state.

6.tOW and tWHZ are specified with CL = 5pF. Transition is measured ±500mV from steady state.

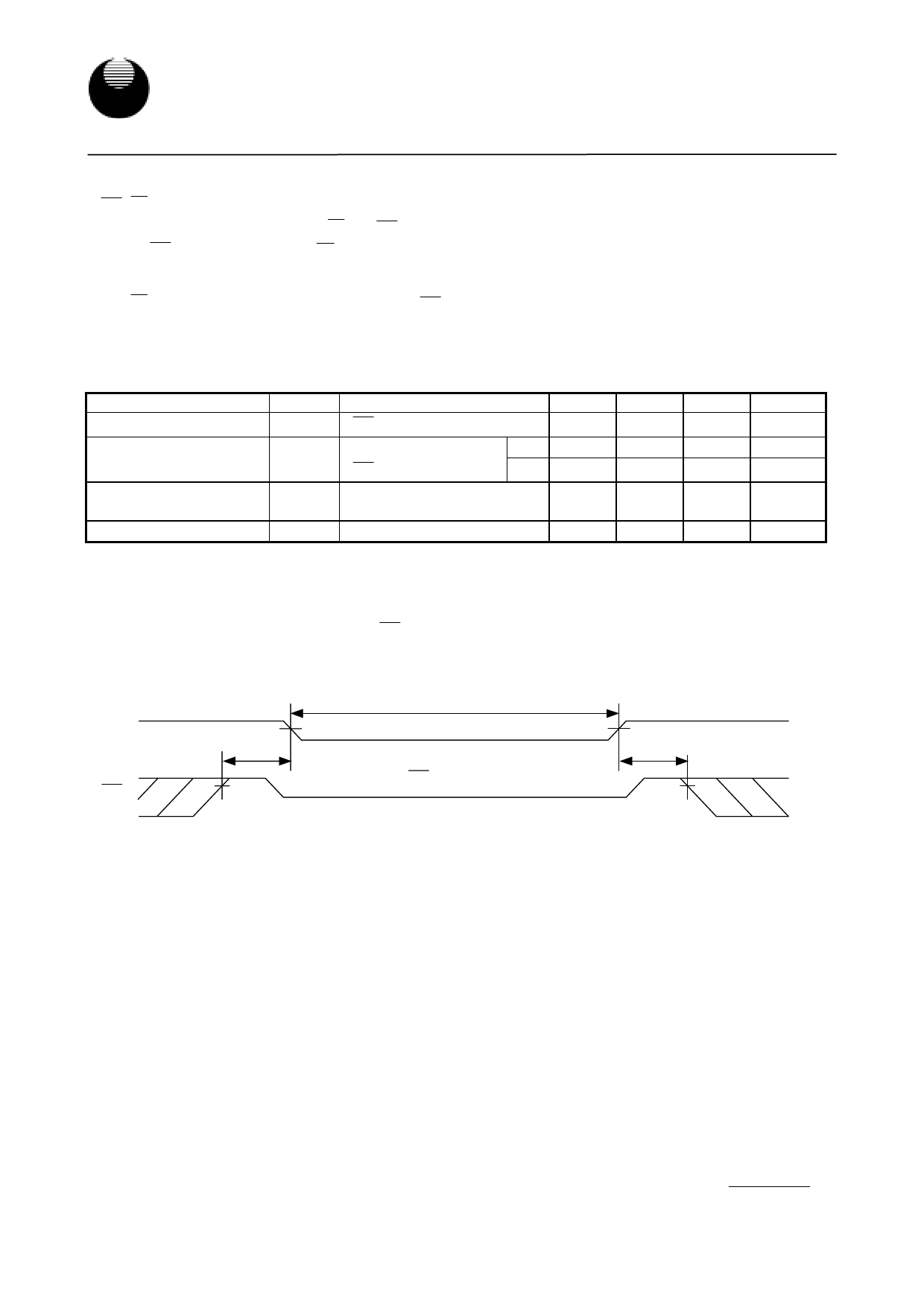

DATA RETENTION CHARACTERISTICS (TA = 0℃ to 70℃)

PARAMETER

Vcc for Data Retention

Data Retention Current

Chip Disable to Data

Retention Time

Recovery Time

tRC* = Read Cycle Time

SYMBOL TEST CONDITION

VDR

CE ≧ VCC-0.2V

IDR

Vcc=3V

CE ≧ VCC-0.2V

tCDR See Data Retention

Waveforms (below)

tR

DATA RETENTION WAVEFORM

MIN.

2.0

-L

-

- LL -

0

tRC*

TYP.

-

1

0.5

-

-

MAX.

5.5

50

10

-

-

UNIT

V

µA

µA

ns

ns

Low Vcc Data Retention Waveform (1) ( CE controlled)

VCC

CE

Vcc(min.)

tCDR

VIH

VDR ≧ 2V

CE ≧ VCC-0.2V

Vcc(min.)

tR

VIH

_____________________________________________________________________________________________

UTRON TECHNOLOGY INC.

1F, No. 11, R&D Rd. II, Science-Based Industrial Park, Hsinchu, Taiwan, R. O. C.

TEL: 886-3-5777882 FAX: 886-3-5777919

6

P80027