M95320-MB3 데이터 시트보기 (PDF) - STMicroelectronics

부품명

상세내역

일치하는 목록

M95320-MB3 Datasheet PDF : 42 Pages

| |||

M95640, M95320

(BP1, BP0) bits of the Status Register, are

also hardware protected against data

modification.

Regardless of the order of the two events, the

Hardware Protected Mode (HPM) can be entered:

– by setting the Status Register Write Disable

(SRWD) bit after driving Write Protect (W) Low

– or by driving Write Protect (W) Low after

setting the Status Register Write Disable

(SRWD) bit.

The only way to exit the Hardware Protected Mode

(HPM) once entered is to pull Write Protect (W)

High.

If Write Protect (W) is permanently tied High, the

Hardware Protected Mode (HPM) can never be

activated, and only the Software Protected Mode

(SPM), using the Block Protect (BP1, BP0) bits of

the Status Register, can be used.

Table 8. Address Range Bits

Device

32 Kbit

Devices

64 Kbit

Devices

Address Bits

A12-A0

A11-A0

Note: b15 to b13 are Don’t Care on the 64 Kbit devices.

b15 to b12 are Don’t Care on the 32 Kbit devices.

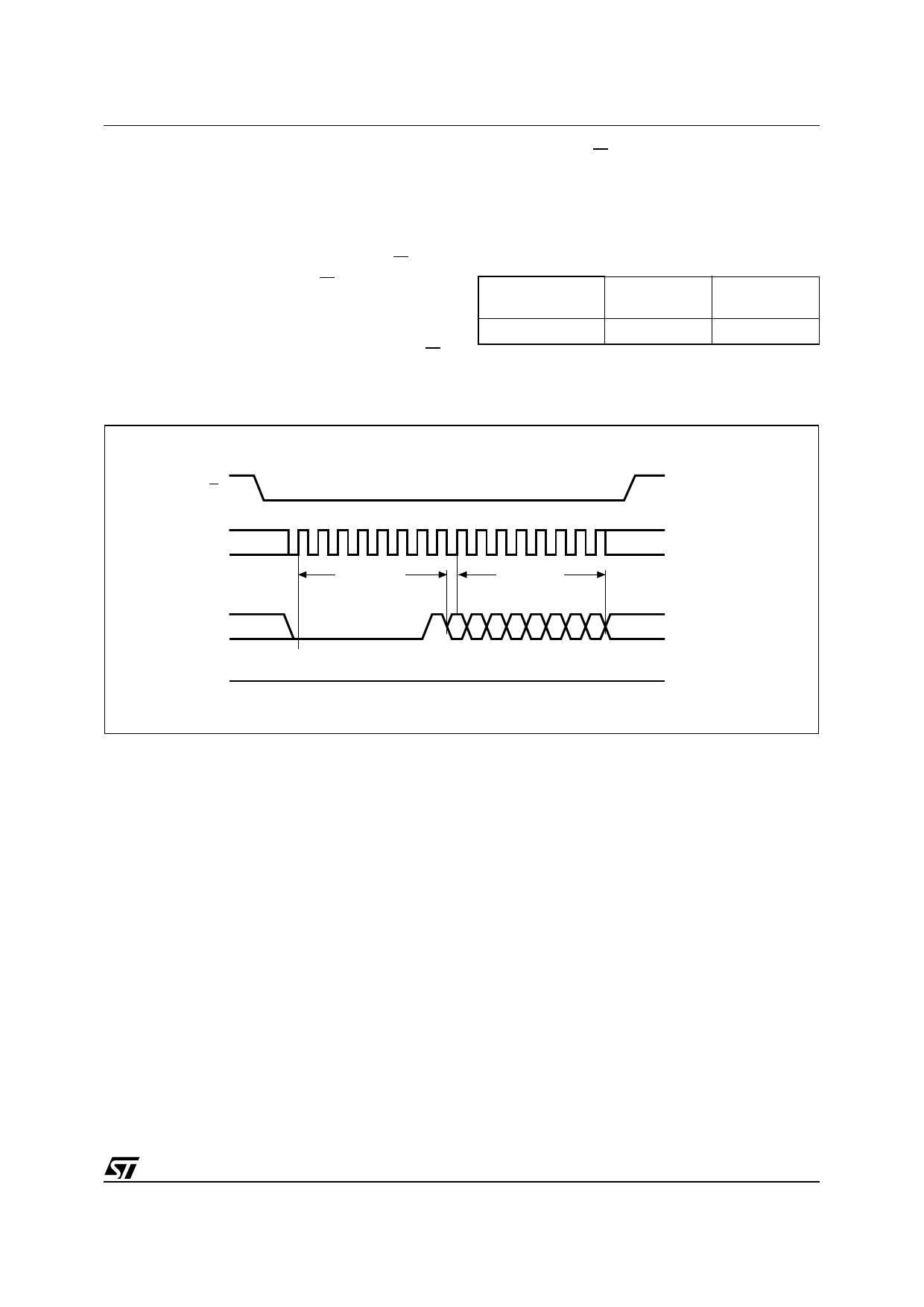

Figure 11. Write Status Register (WRSR) Sequence

S

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

C

Instruction

Status

Register In

D

76543210

High Impedance

MSB

Q

AI02282D

17/42