ALC892 데이터 시트보기 (PDF) - Realtek Semiconductor

부품명

상세내역

일치하는 목록

ALC892 Datasheet PDF : 90 Pages

| |||

ALC892

Datasheet

7.1.1.

Item

BCLK

SYNC

SDO

SDI

RST#

Link Signal Definitions

Table 2. Link Signal Definitions

Description

24.0MHz bit clock sourced from the HDA controller and connecting to all codecs

48kHz signal used to synchronize input and output streams on the link. It is sourced from the HDA

controller and connects to all codecs

Serial data output signal driven by the HDA controller to all codecs. Commands and data streams are carried

on SDO. The data rate is double pumped; the controller drives data onto the SDO, the codec samples data

present on SDO with respect to each edge of BCLK. The HDA controller must support at least one SDO. To

extend outbound bandwidth, multiple SDOs may be supported

Serial data input signal driven by the codec. This is point-to-point serial data from the codec to the HDA

controller. The controller must support at least one SDI, and up to a maximum of 15 SDI’s can be supported.

SDI is driven by the codec at each rising edge of BCLK, and sampled by the controller at each rising edge of

BCLK. SDI can be driven by the controller to initialize the codec’s ID

Active low reset signal. Asserted to reset the codec to default power on state. RST# is sourced from the HDA

controller and connects to all codecs

Signal Name

BCLK

SYNC

SDO

SDI

RST#

Source

Controller

Controller

Controller

Codec/Controller

Controller

Table 3. HDA Signal Definitions

Type for Controller Description

Output

Global 24.0MHz Bit Clock

Output

Global 48kHz Frame Sync and Outbound Tag Signal

Output

Serial Data Output from the Controller

Input/Output Serial Data Input from Codec.

Weakly pulled down by the controller

Output

Global Active Low Reset Signal

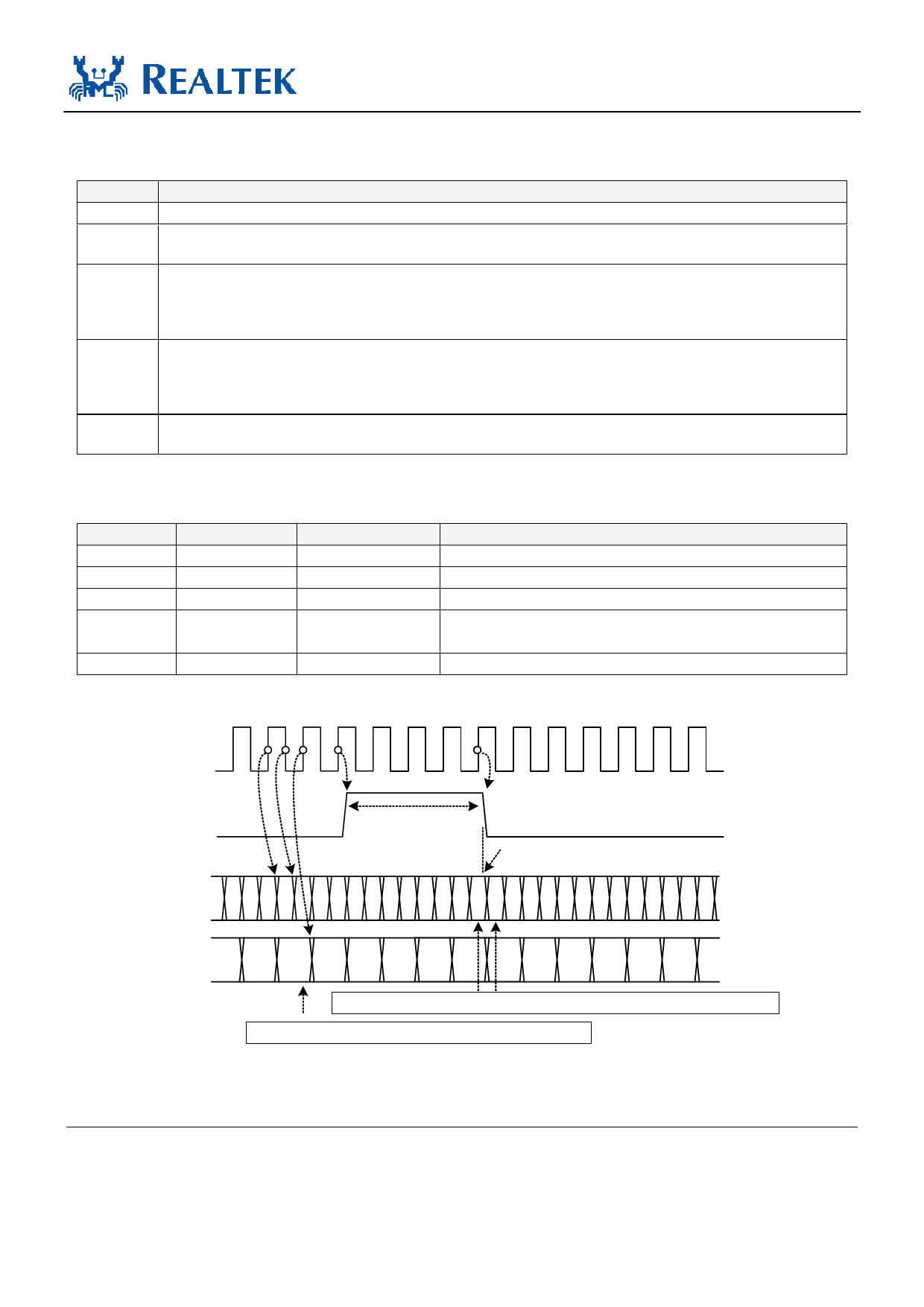

BCLK

SYNC

SDO

SDI

8-Bit Frame SYNC

Start of Frame

7 6 5 4 3 2 1 0 999 998 997 996 995 994 993 992 991 990

3

2

10

499 498 497 496 495 494

Codec samples SDO at both rising and falling edge of BCLK

Controller samples SDI at rising edge of BCLK

Figure 5. Bit Timing

7.1+2 Channel HD Audio Codec with Content Protection 11

Track ID: JATR-2265-11 Rev. 1.3