CS4222 데이터 시트보기 (PDF) - Cirrus Logic

부품명

상세내역

일치하는 목록

CS4222 Datasheet PDF : 26 Pages

| |||

CS4222

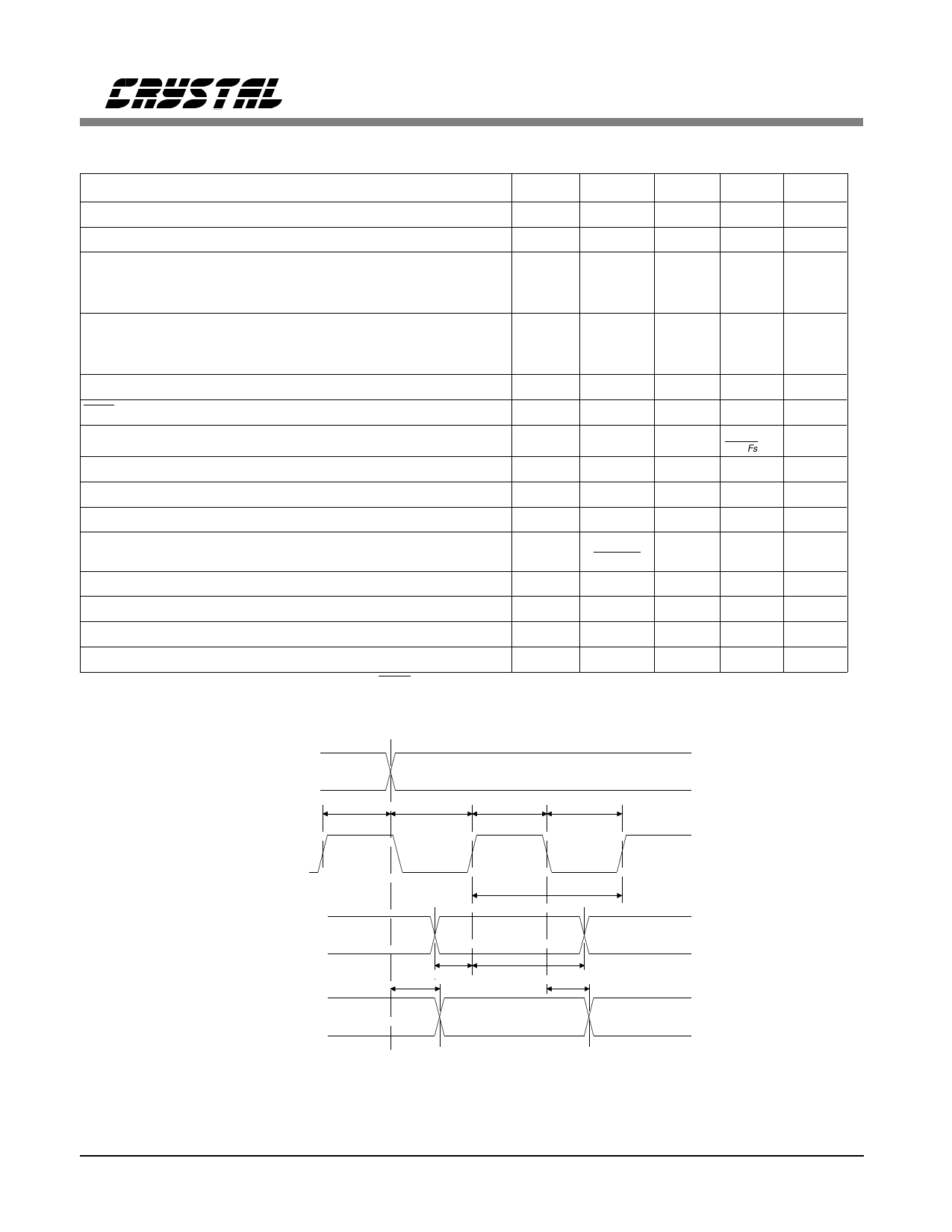

SWITCHING CHARACTERISTICS (TA = 25°C; VA, VD = +5V ±5%, outputs loaded with 30pF)

Parameter

Symbol Min

Typ Max Units

Audio ADC’s & DAC’s Sample Rate

Fs

4

-

50

kHz

MCLK Frequency

(MCLK = 256, 384, or 512 Fs)

1.024

-

26 MHz

MCLK Pulse Width High

MCLK = 512 Fs

MCLK = 384 Fs

MCLK = 256 Fs

10

-

-

ns

21

-

-

ns

31

-

-

ns

MCLK Pulse Width Low

MCLK = 512 Fs

MCLK = 384 Fs

MCLK = 256 Fs

10

-

-

ns

21

-

-

ns

31

-

-

ns

MCLK Jitter Tolerance

-

500

- ps RMS

RST Low Time

(Note 8)

10

-

-

ms

SCLK Falling edge to SDOUT output valid (DSCK=0)

tdpd

-

-

1

(384)Fs

+

20

ns

LRCK edge to MSB valid

tlrpd

-

-

25

ns

SDIN Setup Time Before SCLK Rising Edge

(DSCK=0) tds

-

-

25

ns

SDIN Hold Time After SCLK Rising Edge

SCLK Period

(DSCK=0) tdh

-

-

tsckw

1

-

(128) Fs

25

ns

-

ns

SCLK High Time

tsckh

40

-

-

ns

SCLK Low Time

tsckl

40

-

-

ns

SCLK Rising to LRCK Edge

(DSCK=0) tlrckd

20

-

-

ns

LRCK Edge to SCLK Rising

(DSCK=0) tlrcks

40

-

-

ns

Notes: 8. After powering up the CS4222, PDN should be held low for 10 ms to allow the power supply

to settle.

LRCK

SCLK*

t lrckd

t lrcks

t sckh

tsckl

t sckw

SDIN

SDOUT

tlrpd tds

tdh

MSB

tdpd

MSB-1

*SCLK shown for DSCK = 0, SCLK inverted for DSCK = 1.

Serial Audio Port Data I/O timing

4

DS236PP3