MC74HCT174A 데이터 시트보기 (PDF) - Motorola => Freescale

부품명

상세내역

일치하는 목록

MC74HCT174A

MC74HCT174A Datasheet PDF : 5 Pages

| |||

MC74HCT174A

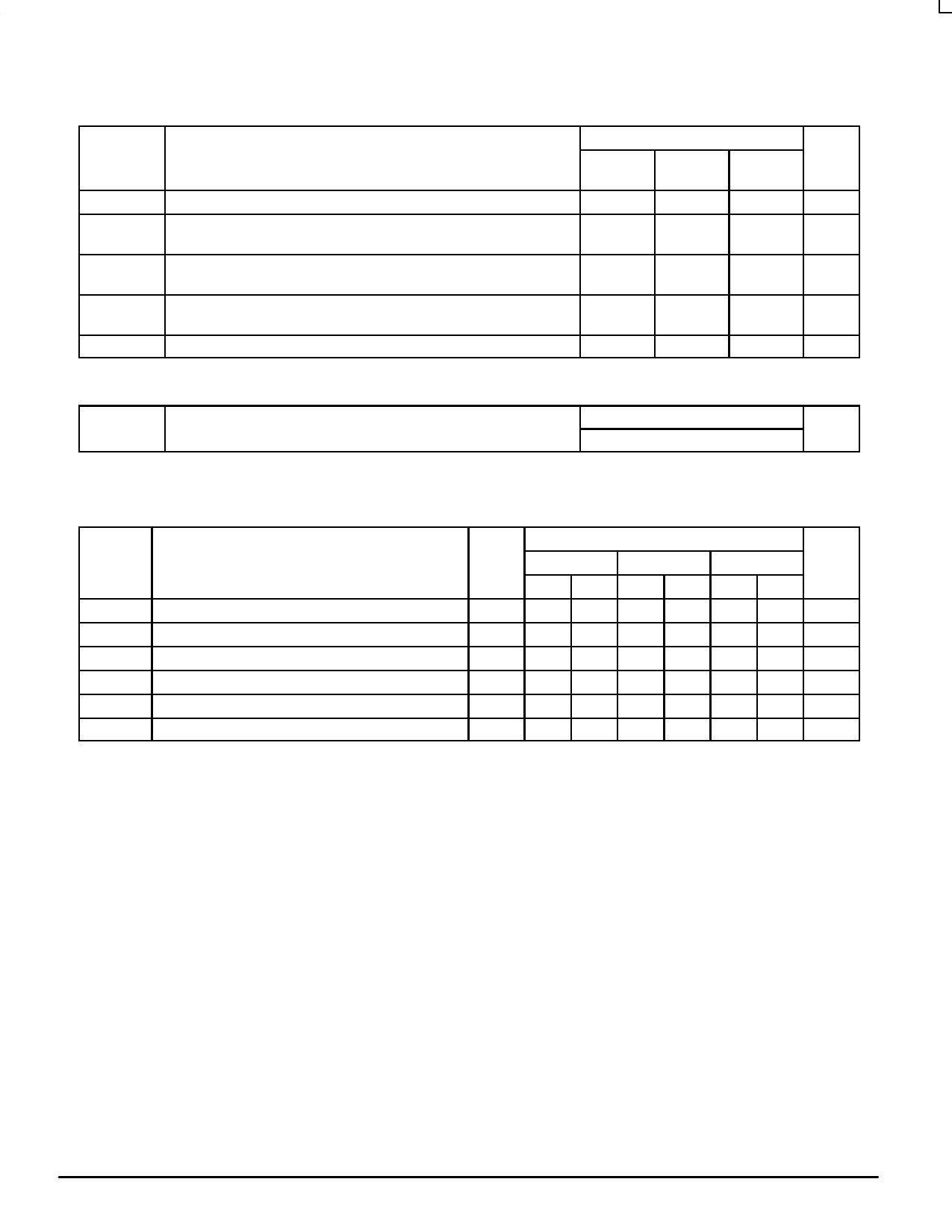

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ AC ELECTRICAL CHARACTERISTICS (VCC = 5.0 V ± 10%, CL = 50 pF, Input tr = tf = 6.0 ns)

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Guaranteed Limit

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Symbol

Parameter

– 55 to

25_C

v v 85_C

125_C Unit

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ fMAX

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tPLH,

tPHL

Maximum Clock Frequency (50% Duty Cycle)

Maximum Propagation Delay, Clock to Q

(Figures 1 and 4)

30

24

20

MHz

24

30

36

ns

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tPHL

Maximum Propagation Delay, Reset to Q

(Figures 2 and 4)

23

28

35

ns

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tTLH,

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tTHL

Maximum Output Transition Time, Any Output

(Figures 1 and 4)

15

19

22

ns

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Cin

Maximum Input Capacitance

10

10

10

pF

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ NOTE: For propagation delays with loads other than 50 pF, and information on typical parametric values, see Chapter 2 of the Motorola High–

Speed CMOS Data Book (DL129/D).

Typical @ 25°C, VCC = 5.0 V

CPD

Power Dissipation Capacitance (Per Enabled Output)*

79

pF

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ * Used to determine the no–load dynamic power consumption: PD = CPD VCC2f + ICC VCC. For load considerations, see Chapter 2 of the

Motorola High–Speed CMOS Data Book (DL129/D).

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ TIMING REQUIREMENTS (VCC = 5.0 V ± 10%, CL = 50 pF, Input tr = tf = 6.0 ns)

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Guaranteed Limit

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ – 55 to 25_C

v 85_C

v 125_C

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Symbol

Parameter

Fig. Min Max Min Max Min Max Unit

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tsu

Minimum Setup Time, Data to Clock

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ th

Minimum Hold Time, Clock to Data

3

10

13

15

ns

3

5.0

6.0

8.0

ns

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ trec

Minimum Recovery Time, Reset Inactive to Clock

2

5.0

6.0

8.0

ns

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tw

Minimum Pulse Width, Clock

1

15

19

22

ns

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tw

Minimum Pulse Width, Reset

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tr, tf

Maximum Input Rise and Fall Times

2

15

19

22

ns

1

500

500

500

ns

High–Speed CMOS Logic Data

3

DL129 — Rev 6

MOTOROLA