MX8335 데이터 시트보기 (PDF) - Macronix International

부품명

상세내역

일치하는 목록

MX8335 Datasheet PDF : 6 Pages

| |||

MX8335

FUNCTIONAL DESCRIPTION

The Rambus clock generator is an integrated circuit of the

phase locked loop frequency synthesizer. It provides two

clock outputs for dual Rambus channel systems.

As shown in the block diagram, a phase locked loop

consists of dividers, phase frequency comparator(PFC),

charge pump, voltage controlled oscillator(VCO), and

loop filter. All components for PLL are integrated inside

the chip.

The dividers provide a fixed multiplication ratio 40/3.

When a reference clock, ranging from 15MHz to 20MHz

and either coming from crystal or external system refer-

ence, provides to PLL, the clock outputs should fall in the

range of 200-266.67MHz. Following examples shows the

relationship between input and output frequencies:

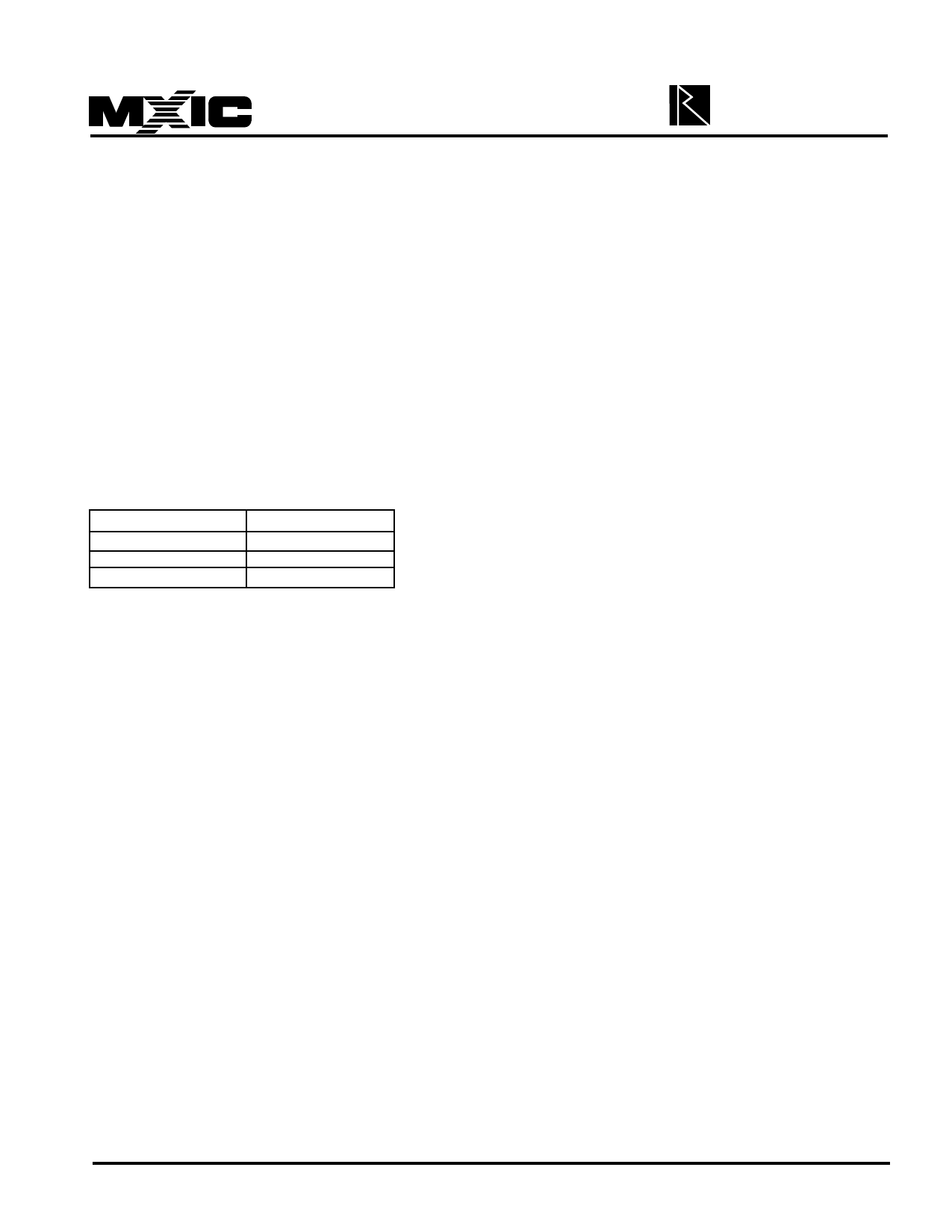

Reference Frequency

15MHz

18.75MHz

20MHz

Output Frequency

200MHz

250MHz

266.67MHz

FREQUENCY REFERENCE

The internal reference oscillator includes all passive

components required. A proper resonant crystal should

be connected between XO and XI. To minimize the noise

pick up, maintain short lead lengths between the crystal

and the MX8335 by soldering the crystal to the ground

plane. The lead length of the capacitor should be kept to

minimum to reduce noise suscepibility. The reference

clock can also be supplied by external clock signal. In this

case, the reference clock should connected to XI and XO

should be unconnected.

POWER SUPPLY CONDITIONING

Clock jittering is the undesirable variations in frequency

and phase of a clock source. In PLL, there are many clock

jitter sources, such as flicker and thermal noise in elec-

tronic element, electromagnetic coupling, power supply

noise, signal reflection, ground bounce, physical

vibration and variation in temperature and humidity.

Among these noise factors, the power supply noise and

ground bounce are most crucial and should be given

special care. To eliminate the supply noise, it is judicious

to decouple the power noise as shown in Fig. 1, where

C1=0.01uF, C2=0.1uF, and C3=47uF.

OUTPUT CIRCUITRY

The clock source output is an open drain NMOS transis-

tor. The MX8335 enables and disables the NMOS

transistor alternately to drive the output load. The biasing

circuity for the MX8335 is shown in Fig. 1.

Output high voltage is determined by the Vt voltage. To

set a value for output low voltage, we must determine the

Rs and Rt values. Rt is determined by system operating

conditions, which may be ranging from 25 Ohms to 50

Ohms. Rs can be acquired by following equation:

Rs=(Rt x Vt/Vs)-(Rt+Ro)

Ro=On resistor of NMOS transistor

Vs=Signal Swing

For a system with Vt=2.5V, Rt=25 Ohms, Vs=1.4V, and

the MX8335's Ro=10 Ohms

Rs=(25 x 2.5/1.4)-(25+10)=9.6 Ohms

Cx capacitor can help equalize rising and falling rate. Rx

resistor helps decrease the rising time. Both Rx and Cx

depend on Rt+Rs and PCB layout. Typical values of Rx

and Cx for 25 Ohms line impedance are ∞ Ohms and 4pF

respectively. For 50 Ohms line impedance, Rx is about

100 Ohms, and Cx is about 2pF. Special care must be

taken during physical design of the output bias circuits

and the Rambus channel.

Rx, Cx, and Rs should be as close to the MX8335 as

possible, and are prefered to use SMD devices. The

signal path must be built using controlled impedence

transmission line technique.

2