M38B57MFH-XXXXFP 데이터 시트보기 (PDF) - MITSUBISHI ELECTRIC

부품명

상세내역

일치하는 목록

M38B57MFH-XXXXFP Datasheet PDF : 355 Pages

| |||

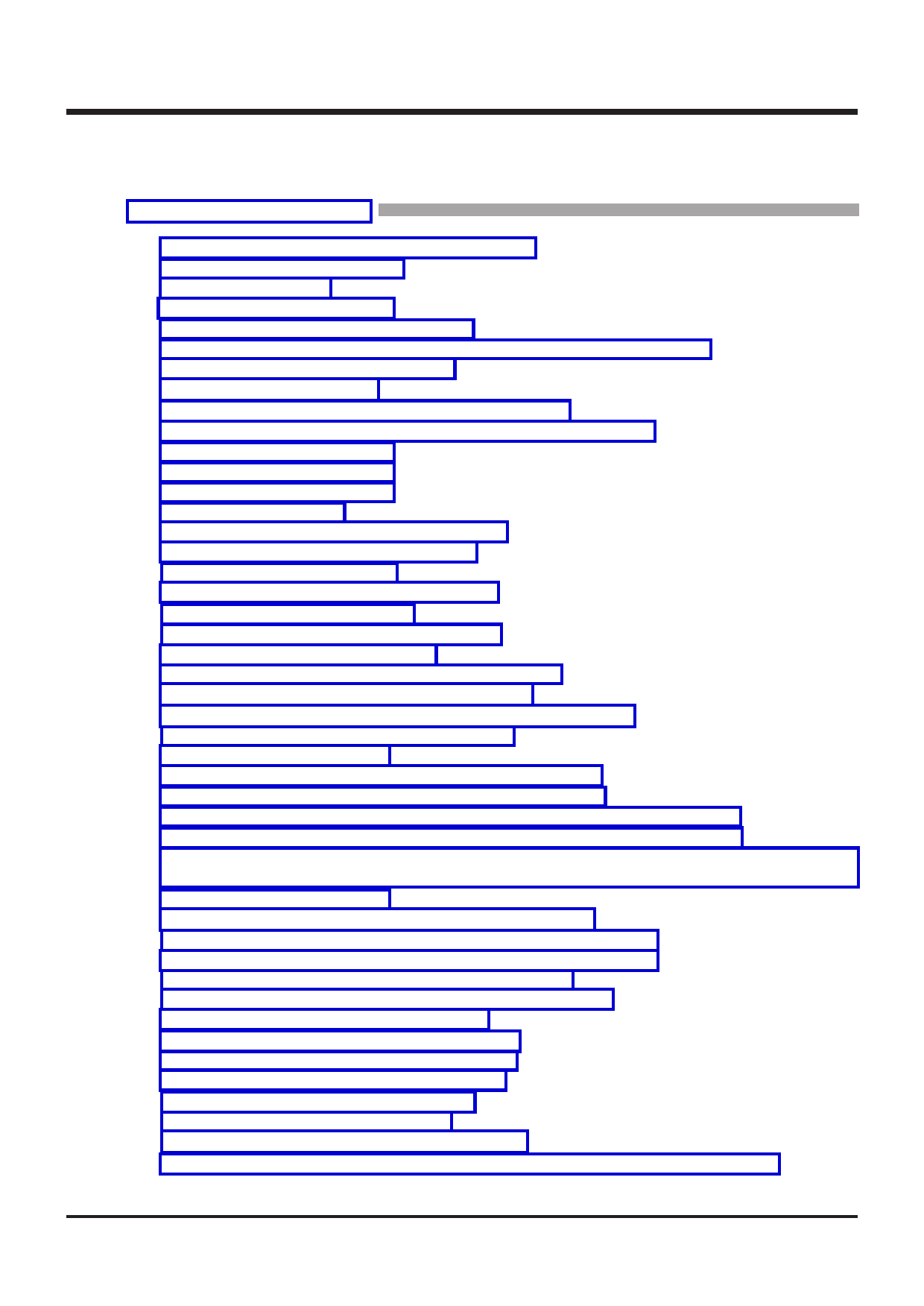

List of figures

List of figures

CHAPTER 1 HARDWARE

Fig. 1 Pin configuration of M38B5xMxH-XXXXFP ..................................................................... 1-2

Fig. 2 Functional block diagram ................................................................................................... 1-3

Fig. 3 Part numbering .................................................................................................................... 1-6

Fig. 4 Memory expansion plan ..................................................................................................... 1-7

Fig. 5 740 Family CPU register structure ................................................................................... 1-8

Fig. 6 Register push and pop at interrupt generation and subroutine call ........................... 1-9

Fig. 7 Structure of CPU mode register ..................................................................................... 1-11

Fig. 8 Memory map diagram ...................................................................................................... 1-12

Fig. 9 Memory map of special function register (SFR) .......................................................... 1-13

Fig. 10 Structure of pull-up control registers (PULL1 and PULL2) ...................................... 1-14

Fig. 11 Port block diagram (1) ................................................................................................... 1-17

Fig. 12 Port block diagram (2) ................................................................................................... 1-18

Fig. 13 Port block diagram (3) ................................................................................................... 1-19

Fig. 14 Interrupt control ............................................................................................................... 1-22

Fig. 15 Structure of interrupt related registers ........................................................................ 1-22

Fig. 16 Structure of timer related register ................................................................................ 1-23

Fig. 17 Block diagram of timer .................................................................................................. 1-24

Fig. 18 Timing chart of timer 6 PWM1 mode ........................................................................... 1-25

Fig. 19 Block diagram of timer X .............................................................................................. 1-27

Fig. 20 Structure of timer X related registers .......................................................................... 1-27

Fig. 21 Block diagram of serial I/O1 ......................................................................................... 1-28

Fig. 22 Structure of serail I/O1 control registers 1, 2 ............................................................ 1-29

Fig. 23 Structure of serial I/O1 control register 3 ................................................................... 1-30

Fig. 24 Structure of serial I/O1 automatic transfer data pointer ........................................... 1-31

Fig. 25 Automatic transfer serial I/O operation ....................................................................... 1-32

Fig. 26 SSTB1 output operation .................................................................................................... 1-33

Fig. 27 SBUSY1 input operation (internal synchronous clock) ................................................... 1-33

Fig. 28 SBUSY1 input operation (external synchronous clock) .................................................. 1-33

Fig. 29 SBUSY1 output operation (internal synchronous clock, 8-bits serial I/O) ................... 1-34

Fig. 30 SBUSY1 output operation (external synchronous clock, 8-bits serial I/O) .................. 1-34

Fig. 31 SBUSY1 output operation in automatic transfer serial I/O mode (internal synchronous

clock, SBUSY1 output function outputs each 1-byte) ................................................... 1-34

Fig. 32 SRDY1 output operation .................................................................................................... 1-35

Fig. 33 SRDY1 input operation (internal synchronous clock) .................................................... 1-35

Fig. 34 Handshake operation at serial I/O1 mutual connecting (1) ...................................... 1-36

Fig. 35 Handshake operation at serial I/O1 mutual connecting (2) ...................................... 1-36

Fig. 36 Block diagram of clock snchronous serial I/O2 ......................................................... 1-37

Fig. 37 Operation of clock synchronous serial I/O2 function ................................................ 1-37

Fig. 38 Block diagram of UART serial I/O2 ............................................................................. 1-38

Fig. 39 Operation of UART serial I/O2 function ...................................................................... 1-38

Fig. 40 Structure of serial I/O2 related register ...................................................................... 1-39

Fig. 41 Block diagram for FLD control circuit .......................................................................... 1-40

Fig. 42 Structure of FLDC mode register ................................................................................. 1-41

Fig. 43 Segment/Digit setting example ..................................................................................... 1-42

Fig. 44 FLD automatic display RAM assignment .................................................................... 1-43

Fig. 45 Example of using FLD automatic display RAM in 16-timing•ordinary mode ......... 1-44

38B5 Group User’s Manual

i