AD74322AAR 데이터 시트보기 (PDF) - Analog Devices

부품명

상세내역

일치하는 목록

AD74322AAR Datasheet PDF : 20 Pages

| |||

PRELIMINARY TECHNICAL DATA

AD74322

FILTER

2.4 V

3.3 V

DUAL

REGULATOR

5.0 V

AVDD

VDD2

VDD1

DVDD

4

AD743xx

4

DSP

Y AGND

DGND

DGND

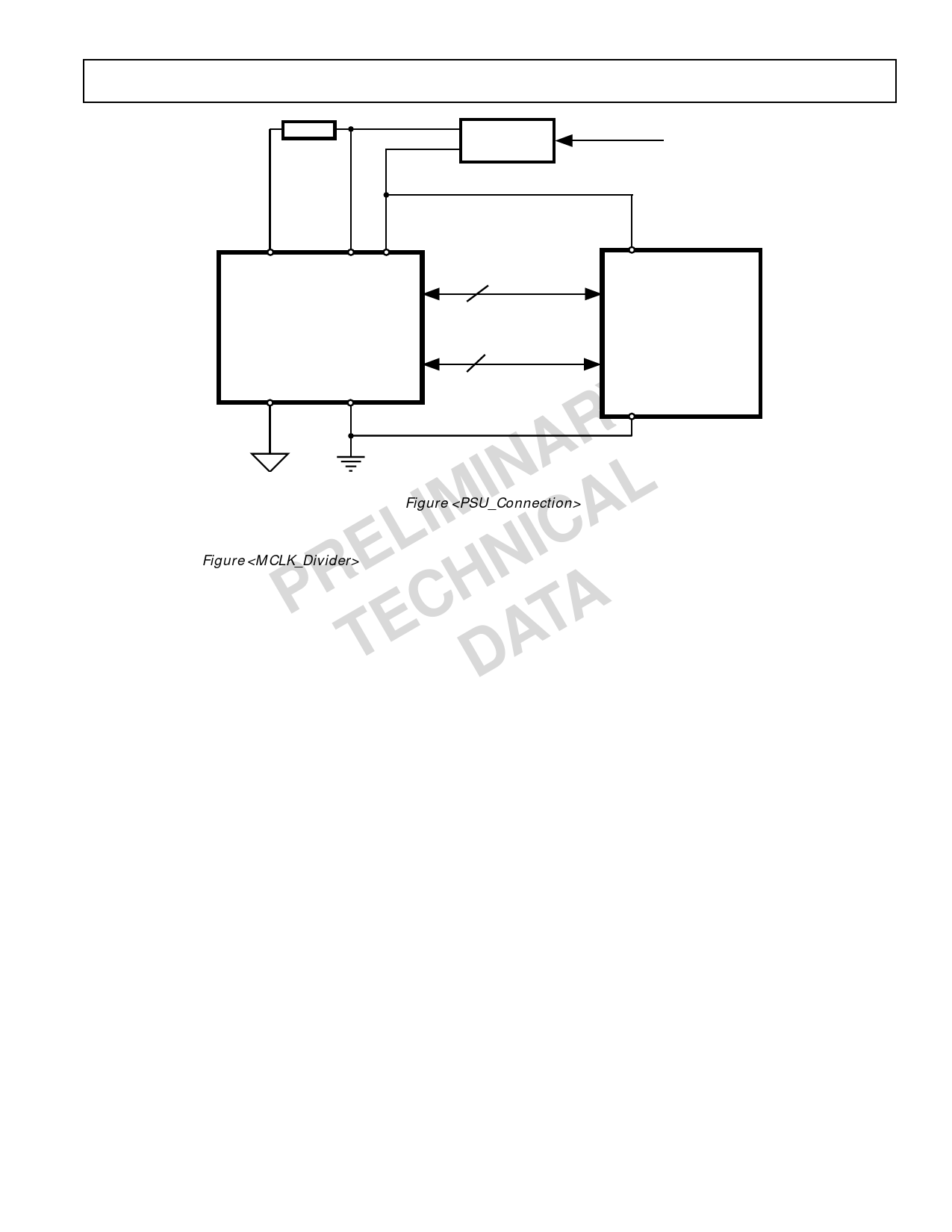

INAR L Figure <PSU_Connection>

LIM ICA Figure<MCLK_Divider>

E N The divider ratios will allow more convenient sample rate

PR H selection from a common MCLK which may be required

C A in many voice related applications.

E T Example 1: fSAMP = 48 kHz and 8 kHz required

T A MCLK = 48*103 * 256 = 12.288 MHz to cater for 48

D kHz fSAMP

a known state following the power-up of the device. There

is also a software reset capability available by setting the

RESET bit in Control Register _. This control register is

accessed through the Control Port.

Power Supplies and Grounds

The AD74322 features three separate supplies: AVDD,

DVDD1 and DVDD2.

For fSAMP = 8 kHz, it is necessary to use the /3 setting in

Pre-Scaler 1, the /2 setting in Pre-Scaler 2 and pass

AVDD is the supply to the analog section of the device

and must therefore be of sufficient quality to preserve the

through in Pre-Scaler 3. This results in an IMCLK =

AD74322’s performance characteristics. It is nominally a

8*103 * 256 = 2.048 MHz (= 12.288 MHz/6).

2.4 V supply.

Example 2: fSAMP = 48 kHz and 32 kHz required

MCLK = 24.576 MHz

DVDD1 is the supply for the digital interface section of

the device. It is fed from the digital supply voltage of the

DSP or controller to which the device is interfaced and

For fSAMP = 48 kHz, it is necessary to use the /2 setting in

Pre-Scaler 1 and the /1 (pass-through) setting in Pre-

allows the AD74322 to interface with devices operating at

supplies of between 2.4 V -5% to 3.3 V + 10%.

Scaler 2 and pass through in Pre-Scaler 3. This results in

an IMCLK = 48*103 * 256 = 12.288 MHz.

DVDD2 is the supply for the digital core of the

AD74322. It is nominally a 2.4 V supply.

For fSAMP = 32 kHz, it is necessary to use the /3 setting in

Pre-Scaler 1 and the /1 (pass-through) setting in Pre-

Scaler 2 and pass through in Pre-Scaler 3. This results in

an IMCLK = 32*103 * 256 = 8.192 MHz.

Example 3: fSAMP = 44.1 kHz and 11.025 kHz required

MCLK = 44.1*103 * 256 = 11.2896 MHz to cater for

44.1 kHz fSAMP

For fSAMP = 11.025 kHz, it is necessary to use the /1 setting in Pre-

Scaler 1 and the /4 setting in Pre-Scaler 2 and pass

through in Pre-Scaler 3. This results in an IMCLK =

11.025*103 * 256 = 2.8224 MHz (= 11.2896 MHz/4).

Sample Rates

For all applications the sampling rate is defined by the internal master

clock frequency (IMCLK) where IMCLK = 256 * fSAMP.

Power-On Reset

The AD74322 features a power-on reset circuit which

ePnrsDures0t3h/a0t0all internal circuitry is reset and initialised to –9–