MC10135FN 데이터 시트보기 (PDF) - Motorola => Freescale

부품명

상세내역

일치하는 목록

MC10135FN Datasheet PDF : 5 Pages

| |||

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

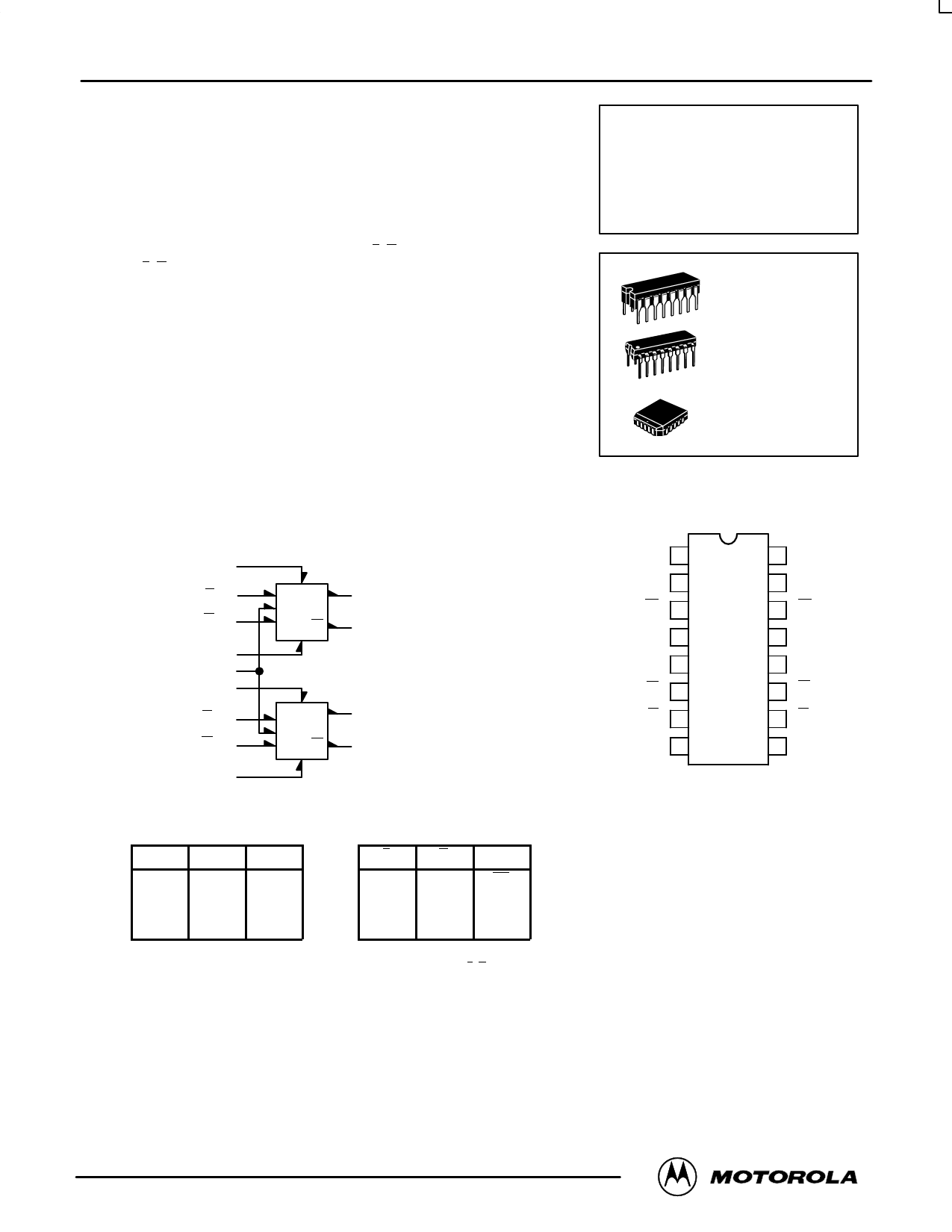

Dual J-K Master-Slave

Flip-Flop

The MC10135 is a dual master–slave dc coupled J–K flip–flop. Asynchro–

nous set (S) and reset (R) are provided. The set and reset inputs override the

clock.

A common clock is provided with separate J–K inputs. When the clock is

static, the J–K inputs do not effect the output.

The output states of the flip–flop change on the positive transition of the

clock.

PD = 280 mW typ/pkg (No Load)

fTog = 140 MHz typ

tpd = 3.0 ns typ

tr, tf = 2.5 ns typ (20%–80%)

MC10135

L SUFFIX

CERAMIC PACKAGE

CASE 620–10

P SUFFIX

PLASTIC PACKAGE

CASE 648–08

FN SUFFIX

PLCC

CASE 775–02

S1 5

J1 7

K1 6

R1 4

C9

S2 12

J2 10

K2 11

R2 13

LOGIC DIAGRAM

Q1

2

Q1

3

VCC1 = PIN 1

VCC2 = PIN 16

VEE = PIN 8

Q2

15

Q2

14

R–S TRUTH TABLE

R

S

Qn+1

L

L

Qn

L

H

H

H

L

L

H

H

N.D.

N.D. = Not Defined

CLOCK J–K TRUTH TABLE*

J

K

Qn+1

L

L

Qn

H

L

L

L

H

H

H

H

Qn

* Output states change on positive

transition of clock for J–K input

condition present.

DIP

PIN ASSIGNMENT

VCC1

1

Q1

2

Q1

3

R1

4

S1

5

K1

6

J1

7

VEE

8

16

VCC2

15

Q2

14

Q2

13

R2

12

S2

11

K2

10

J2

9

C

Pin assignment is for Dual–in–Line Package.

For PLCC pin assignment, see the Pin Conversion

Tables on page 6–11 of the Motorola MECL Data

Book (DL122/D).

3/93

© Motorola, Inc. 1996

3–22

REV 5