SM5852FS 데이터 시트보기 (PDF) - Nippon Precision Circuits

부품명

상세내역

일치하는 목록

SM5852FS Datasheet PDF : 12 Pages

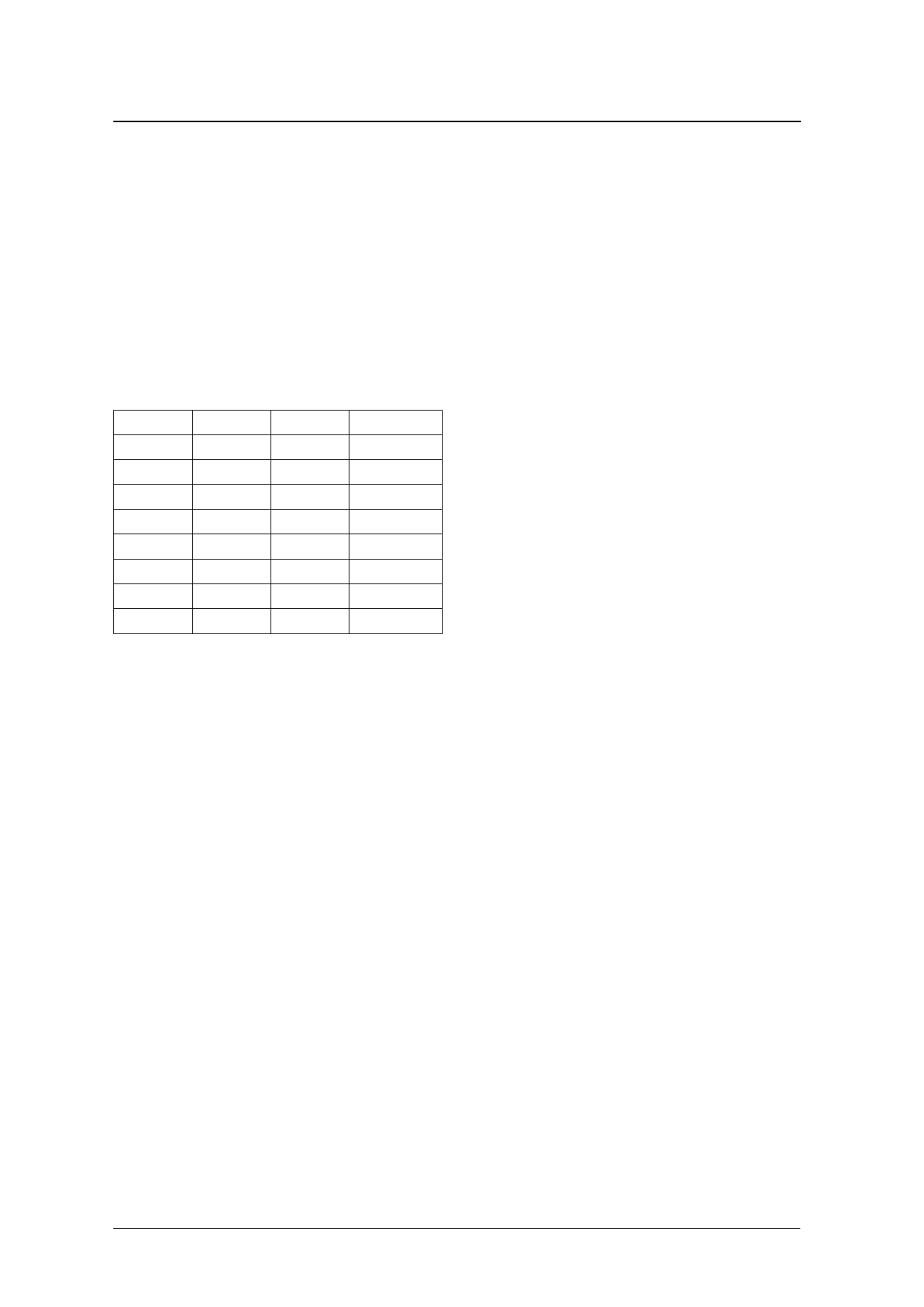

| |||

SM5852FS

FUNCTIONAL DESCRIPTION

DDBB (Digital Dynamic Bass Boost)

The DDBB function emphasizes the low-frequency

components of the input signal by picking out the

low-frequency components and passing them

through a DDBB 3rd-order IIR low-pass filter and

then changing the gain for the low-frequency

components.

Two independent DDBB filters are used, one for

each the left and right channels, to maintain full

channel separation. The DDBB boost is determined

by DB/DS, MOD1 and MOD2.

MOD1

LOW

LOW

LOW

LOW

HIGH

HIGH

HIGH

HIGH

MOD2

LOW

LOW

HIGH

HIGH

LOW

LOW

HIGH

HIGH

DB/DS

LOW

HIGH

LOW

HIGH

LOW

HIGH

LOW

HIGH

Gain mode

18 dB

16 dB

14 dB

12 dB

10 dB

6 dB

Off

Off

Soft Muting

Soft muting is active when MUTEN is LOW. When

MUTEN is LOW, the attenuation changes smoothly

from 0 to −∞ dB in 1024/fs, or approximately 23.2

ms.

When MUTEN goes HIGH, soft muting is released

and the attenuation changes smoothly from −∞ to 0

dB, again taking approximately 23.2 ms.

Also, if a MUTEN transition occurs while the

attenuation is changing, the attenuation then changes

smoothly in the direction specified by the new level

of MUTEN.

DB/DS Switching Shock Noise

The soft muting function is also activated to

eliminate switching shock noise when DB/DS

changes state. When DB/DS changes state, the

attenuation changes to −∞ dB, the internal circuit

settings are activated and then soft muting is

released. Therefore, a maximum time of

approximately 46.4 ms is required to change the

compression mode. Of course, if the attenuation is

already −∞ dB after soft muting using MUTEN, then

no time is required to change compression mode.

Reset Initialization

RSTN should be set LOW at power-ON and after

reacquiring synchronization. Note that if RSTN is

LOW for longer than 1 µs, a through-current flows in

the LSI’s internal dynamic circuits because the

internal clock is stopped. The through-current has no

rated value, so the reset pulse should be kept as short

as possible at all times other than at power-ON.

When RSTN goes from LOW to HIGH, initialization

hold is released and the initialization routine first

resets the internal data over an interval of 4fs. During

the initialization routine, the output data is forcibly

muted so that there is no output signal.

NIPPON PRECISION CIRCUITS—10