UPD780964 데이터 시트보기 (PDF) - NEC => Renesas Technology

부품명

상세내역

일치하는 목록

UPD780964 Datasheet PDF : 42 Pages

| |||

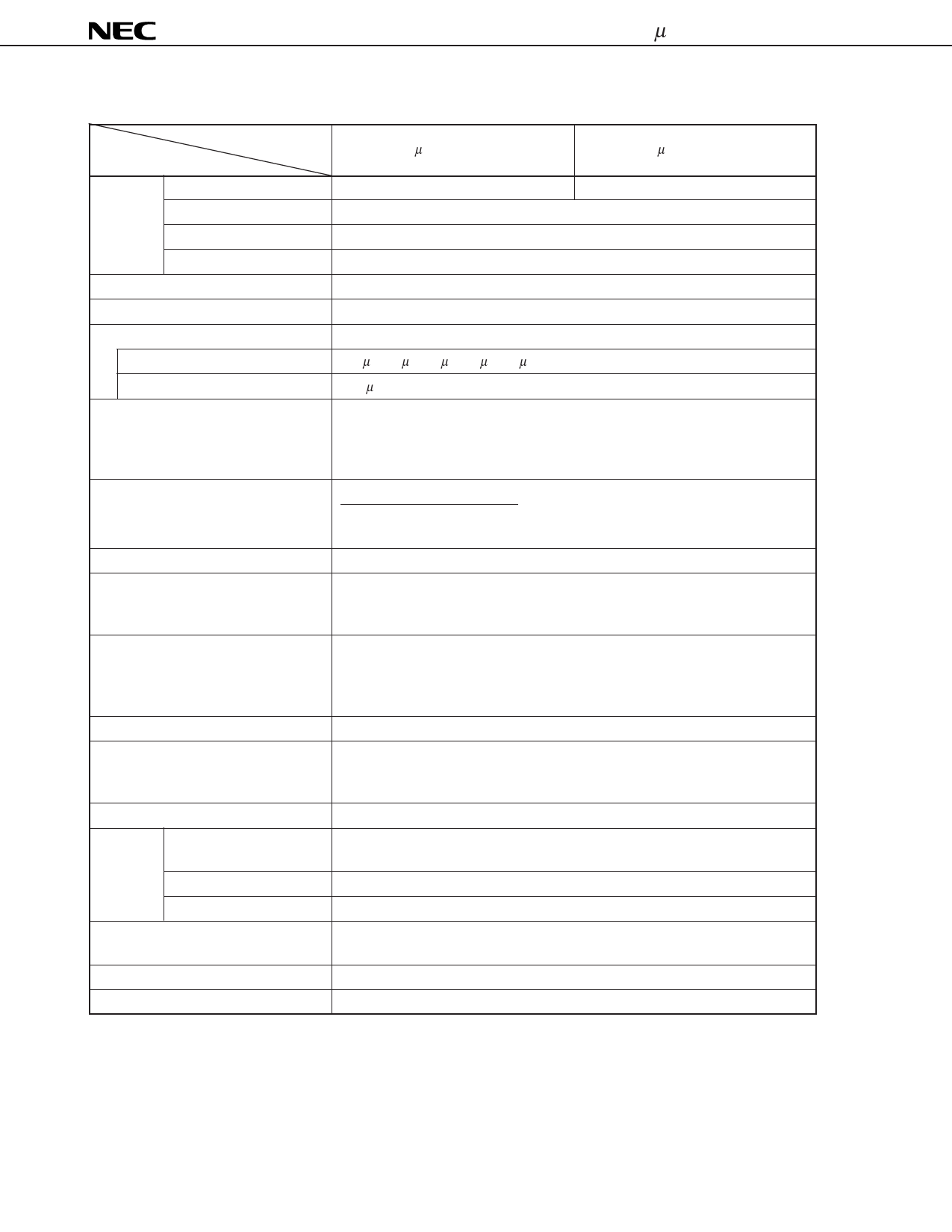

µPD780016Y, 780018Y

OVERVIEW OF FUNCTION

Part Number

Item

Internal ROM

memory Internal high-speed RAM

Buffer RAM

Internal expansion RAM

Memory space

General registers

Instruction cycle

When main system clock selected

When subsystem clock selected

Instruction set

I/O ports

A/D converter

Serial interface

Timer

Timer output

Clock output

Buzzer output

Vectored

interrupt

sources

Maskable

Non-maskable

Software

Test input

Supply voltage

Package

µPD780016Y

µPD780018Y

48K bytes

60K bytes

1024 bytes

32 butes

1024 bytes

64K bytes

8 bits × 32 registers (8 bits × 8 registers × 4 banks)

On-chip instruction execution time selective function

0.4 µs/0.8 µs/1.6 µs/3.2 µs/6.4 µs (at 5.0 MHz)

122 µs (at 32.768 kHz)

• 16-bit operation

• Multiplcation/division (8 bits × 8 bits,16 bits ÷ 8 bits)

• Bit manipulation (set, reset, test, boolean operation)

• BCD adjustment, etc.

Total

: 88

• CMOS input

• CMOS I/O

:9

: 79

• 8-bit resolution × 8 channels

• 3-wire serial I/O mode (with automatic data transmit/receive function): 1 channel

• 3-wire serial I/O mode (with time division transfer function)

: 1 channel

• I2C bus mode (supporting multi-task)

: 1 channel

• 16-bit timer/event counter : 1 channel

• 8-bit timer/event counter : 4 channels

• Watch timer

: 1 channel

• Watchdog timer

: 1 channel

5 (14-bit PWM output × 1, 8-bit PWM output × 2)

39.1 kHz, 78.1 kHz, 156 kHz, 313 kHz, 625 kHz, 1.25 MHz, 2.5 MHz, 5.0 MHz

(at main system clock of 5.0 MHz)

32.768 kHz (at subsystem clock of 32.768 kHz)

2.4 kHz, 4.9 kHz, 9.8 kHz (at main system clock: at 5.0 MHz)

Internal : 12

External : 7

Internal : 1

1

Internal : 1

External : 1

VDD = 2.7 to 5.5 V

• 100-pin plastic QFP (14 × 20 mm)

4