XRT8000IP 데이터 시트보기 (PDF) - Exar Corporation

부품명

상세내역

일치하는 목록

XRT8000IP Datasheet PDF : 24 Pages

| |||

XRT8000

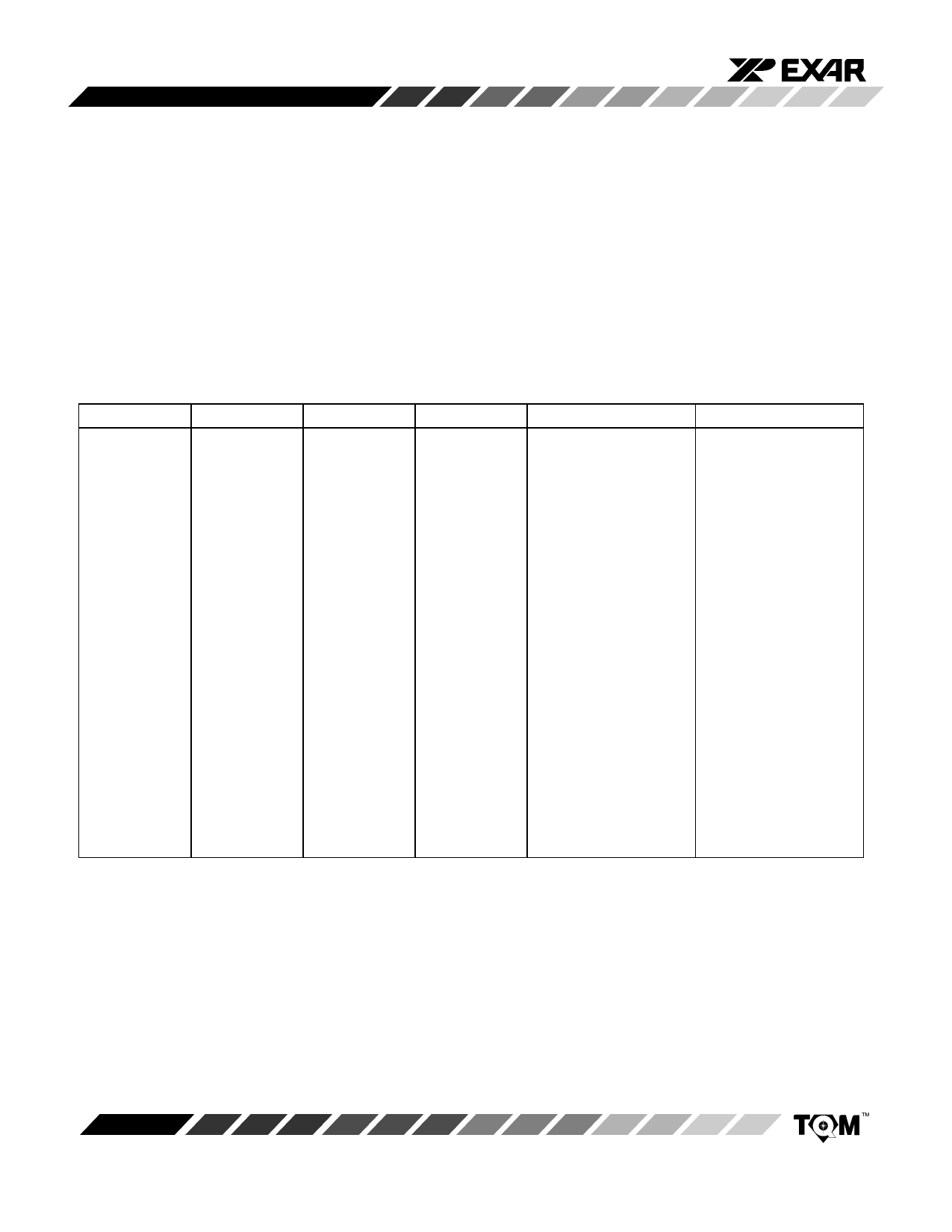

CR2 Register (Power On State = “00000”)

D0 (PL2EN):

Enable control for PLL2. If PL2EN = “1”, then PLL2 is

enabled. Otherwise, if PL2EN = “0”, PLL2 is disabled.

D1~D4 (M1~M4):

Control bits for prescaler divider. These bits will set the

divide ratio of the prescaler such that in MASTER/

FORWARD or REVERSE modes the output of this block

is always at 8kHz. The settings for M4~M1 bits is based

on the input frequency and the mode of operation (which

is determined by the state of IOC4~IOC1 bits) is provided

in Table 3.

M4

M3

M2

M1

0

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

0

1

0

0

0

1

0

1

0

1

1

0

0

1

1

1

1

0

0

0

1

0

0

1

1

0

1

0

1

0

1

1

1

1

0

0

1

1

0

1

1

1

1

0

1

1

1

1

x

x

x

x

x

x

x

x

Note:

This table applies to MASTER (FORWARD, REVERSE) mode only

Table 3. CR2 Register

Mode

Forward

Forward

Forward

Forward

Forward

Forward

Forward

Forward

Forward

Forward

Forward

Forward

Forward

Forward

Forward

Forward

Reverse

Reverse

Input Freq.[kHz]

1x(1544 or 2048)

2x(1544 or 2048)

3x(1544 or 2048)

4x(1544 or 2048)

5x(1544 or 2048)

6x(1544 or 2048)

7x(1544 or 2048)

8x(1544 or 2048)

9x(1544 or 2048)

10x(1544 or 2048)

11x(1544 or 2048)

12x(1544 or 2048)

13x(1544 or 2048)

14x(1544 or 2048)

15x(1544 or 2048)

16x(1544 or 2048)

56

64

Rev. 1.11

10