PCK2020DL 데이터 시트보기 (PDF) - Philips Electronics

부품명

상세내역

일치하는 목록

PCK2020DL Datasheet PDF : 16 Pages

| |||

Philips Semiconductors

CK00 (100/133MHz) spread spectrum

differential system clock generator

Product specification

PCK2020

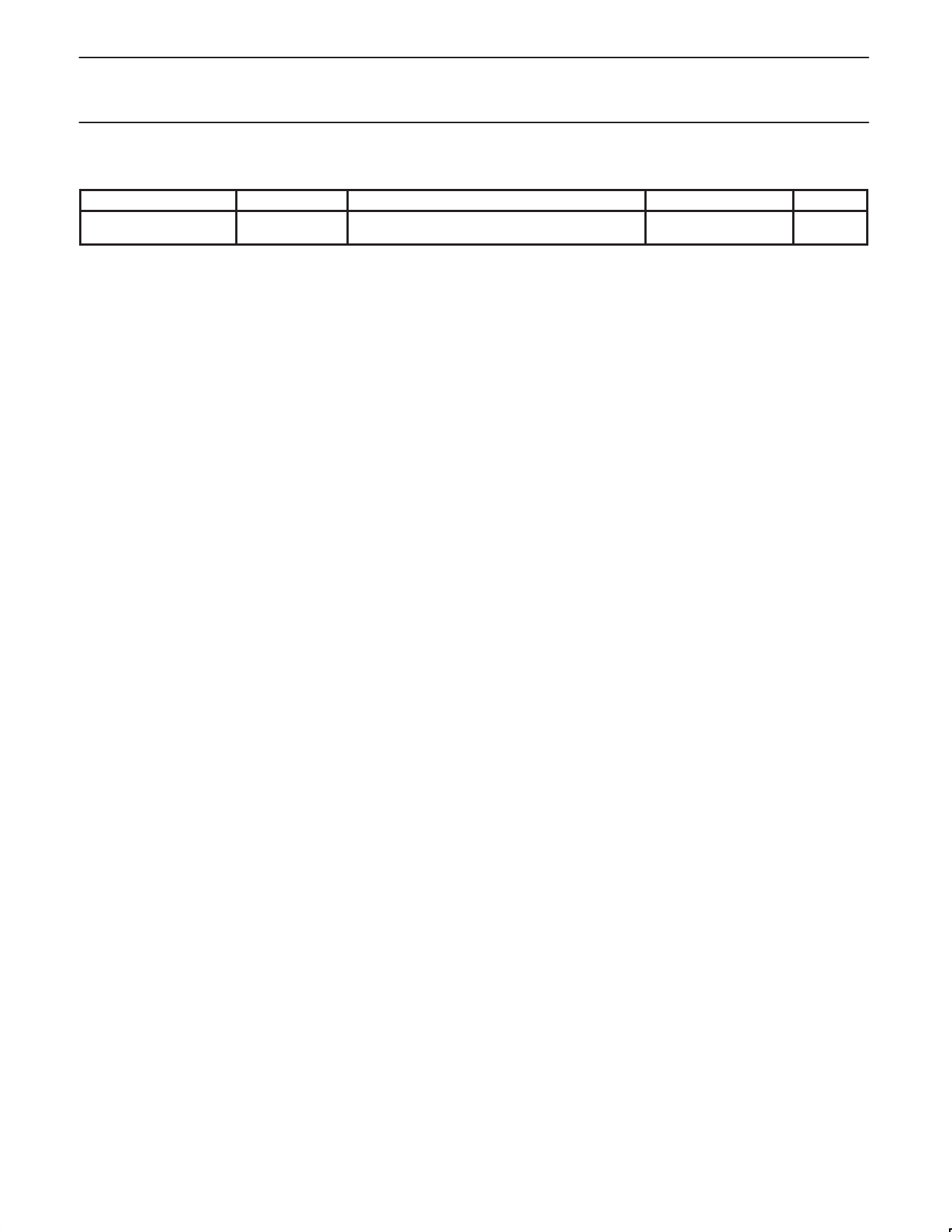

GROUP OFFSET LIMITS

GROUP

OFFSET

MEASUREMENT LOADS (LUMPED)

MEASURE POINTS

NOTES

3V66 to PCI

1.5–3.5 ns

3V66 leads

3V66 @ 30 pf

PCI @ 30 pf

3V66 @ 1.5 V

PCI @ 1.5 V

19, 20

NOTES:

1. Output drivers must have monotonic rise/fall times through the specified VOL/VOH levels.

2. Period, jitter, offset and skew measured on rising edge @ 1.25 V for 2.5 V clocks and @ 1.5 V for 3.3 V clocks.

3. The PCI clock is the Host clock divided by four at Host = 133 MHz. PCI clock is the Host clock divided by three at Host = 100 MHz.

4. 3V66 is internal VCO frequency divided by four for Host = 133 MHz. 3V66 clock is internal VCO frequency divided by three at Host =

100 MHz.

5. THKH is measured at 2.0 V for 2.5 V outputs and 2.4 V for 3.3 V outputs as shown in Figure 7.

6. THKL is measured at 0.4 V for all outputs as shown in Figure 7.

7. The time is specified from when VDDQ achieves its normal operating level (typical condition VDDQ = 3.3 V) until the frequency output is stable

and operating within specification.

8. THRISE and THFALL are measured as a transition through the threshold region VOL = 0.4 V and VOH = 2.4 V (1 mA) JEDEC specification.

9. The average period over any 1 µs period of time must be greater than the minimum specified period.

10. Calculated at minimum edge-rate (1 V/ns) to guarantee 45/55% duty-cycle. Pulse width is required to be wider at faster edge-rate to ensure

duty-cycle specification is met.

11. Test load is Rs = 33.2 Ω, Rp = 49.9 Ω.

12. Must be guaranteed in a realistic system environment.

13. Configured for VOH = 0.71 V in a 50 Ω environment.

14. Measured at crossing points.

15. Measured at 20% to 80%.

16. Determined as a fraction of 2* (Trp–Trn)/(Trp+Trn) where Trp is a rising edge and Trn is an intersecting falling edge.

17. Voltage measure point (Vm = 1.25 V). VDD = 2.5 V.

18. Voltage measure point (Vm = 1.5 V). VDD = 3.3 V.

19. All offsets are to be measured at rising edges.

20. Parameters are guaranteed by design.

2000 Nov 13

11