PCA9544 데이터 시트보기 (PDF) - Philips Electronics

부품명

상세내역

일치하는 목록

PCA9544 Datasheet PDF : 12 Pages

| |||

Philips Semiconductors

4-channel I2C multiplexer and interrupt controller

Product specification

PCA9544

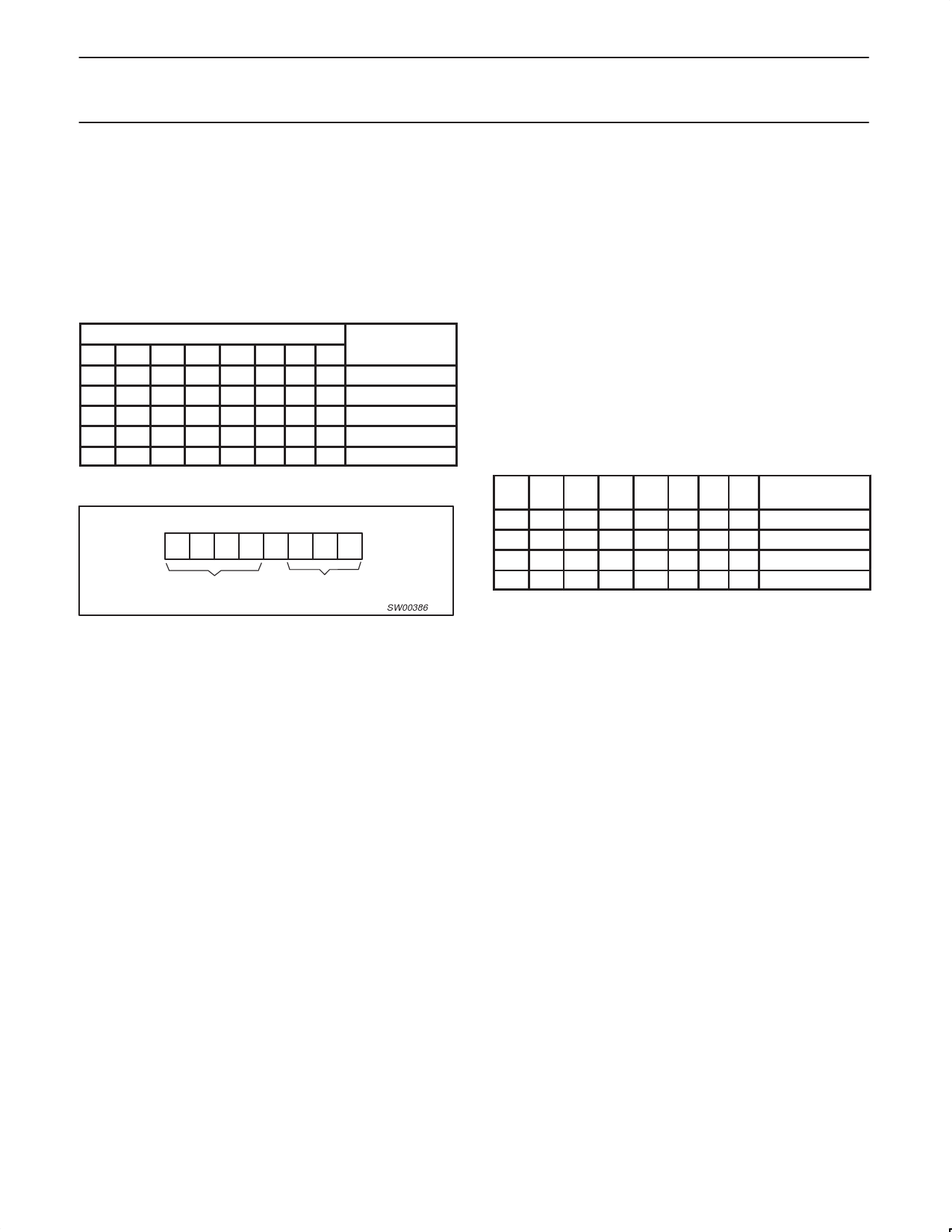

CHANNEL SELECTION

A SC0x/SD0x downstream pair, or channel, is selected by the

contents of the control register. This register is written after the

PCA9544 has been addressed. The 3 LSBs of the control byte are

used to determine which channel is to be selected. When a channel

is selected, the channel will become active after a stop condition has

been placed on the I2C bus. This ensures that all SCx/SDx lines will

be in a HIGH state when the channel is made active, so that no

false conditions are generated at the time of connection.

CONTROL BYTE

7 6 5 4 3 210

X X X X X 0XX

X X X X X 100

X X X X X 101

X X X X X 110

X X X X X 111

SELECTED

CHANNEL

none

0 (SC0/SD0)

1 (SC1/SD1)

2 (SC2/SD2)

3 (SC3/SD3)

CONTROL REGISTER

7 6 5 43 2 1 0

INT3 INT2 INT1 INT0 X B2 B1 B0

Interrupt bits

(read only)

Channel select bits

(read/write)

SW00386

INTERRUPT HANDLING

The PCA9544 provides 4 interrupt inputs, one for each channel and

one open drain interrupt output. When an interrupt is generated by any

device, it will be detected by the PCA9544 and the interrupt output

will be driven LOW. The channel need not be active for detection of

the interrupt. A bit is also set in the control byte. Bits 4 – 7 of the

control byte correspond to channels 0 – 3 of the PCA9544,

respectively. Therefore, if an interrupt is generated by any device

connected to channel 2, then bit 6 will be set in the control register.

Likewise, an interrupt on any device connected to channel 3 would

cause bit 7 of the control register to be set. The master can then

address the PCA 9544 and read the contents of the control byte to

determine which channel contains the device generating the interrupt.

The master can then reconfigure the PCA9544 to select this

channel, and locate the device generating the interrupt and clear it.

The interrupt clears when the device originating the interrupt clears.

It should be noted that more than one device can be providing an

interrupt on a channel, so it is up to the master to ensure that all

devices on a channel are interrogated for an interrupt.

7

6

5

4

3

21

0

INTERRUPTING

CHANNEL

0 0 0 1 X X X X 0 (SC0/SD0)

0 0 1 0 X X X X 1 (SC1/SD1)

0 1 0 0 X X X X 2 (SC2/SD2)

1 0 0 0 X X X X 3 (SC3/SD3)

POWER-ON RESET

During power-up, the control register defaults to all zeroes causing

all the channels to be deselected.

1999 Oct 07

4