NM24C16U 데이터 시트보기 (PDF) - Fairchild Semiconductor

부품명

상세내역

일치하는 목록

NM24C16U Datasheet PDF : 13 Pages

| |||

Write Cycle Timing (Continued)

The NM24C16U/17U device will always respond with an acknowl-

edge after recognition of a start condition and its slave address. If

both the device and a write operation have been selected, the

NM24C16U/17U will respond with an acknowledge after the

receipt of each subsequent eight bit byte.

In the read mode the NM24C16U/17U slave will transmit eight bits

of data, release the SDA line and monitor the line for an acknowl-

edge. If an acknowledge is detected and no stop condition is

generated by the master, the slave will continue to transmit data.

If an acknowledge is not detected, the slave will terminate further

data transmissions and await the stop condition to return to the

standby power mode.

Device Addressing

Following a start condition the master must output the address of

the slave it is accessing. The most significant four bits of the slave

address are those of the device type identifier (see Figure 5). This

is fixed as 1010 for all EEPROM devices.

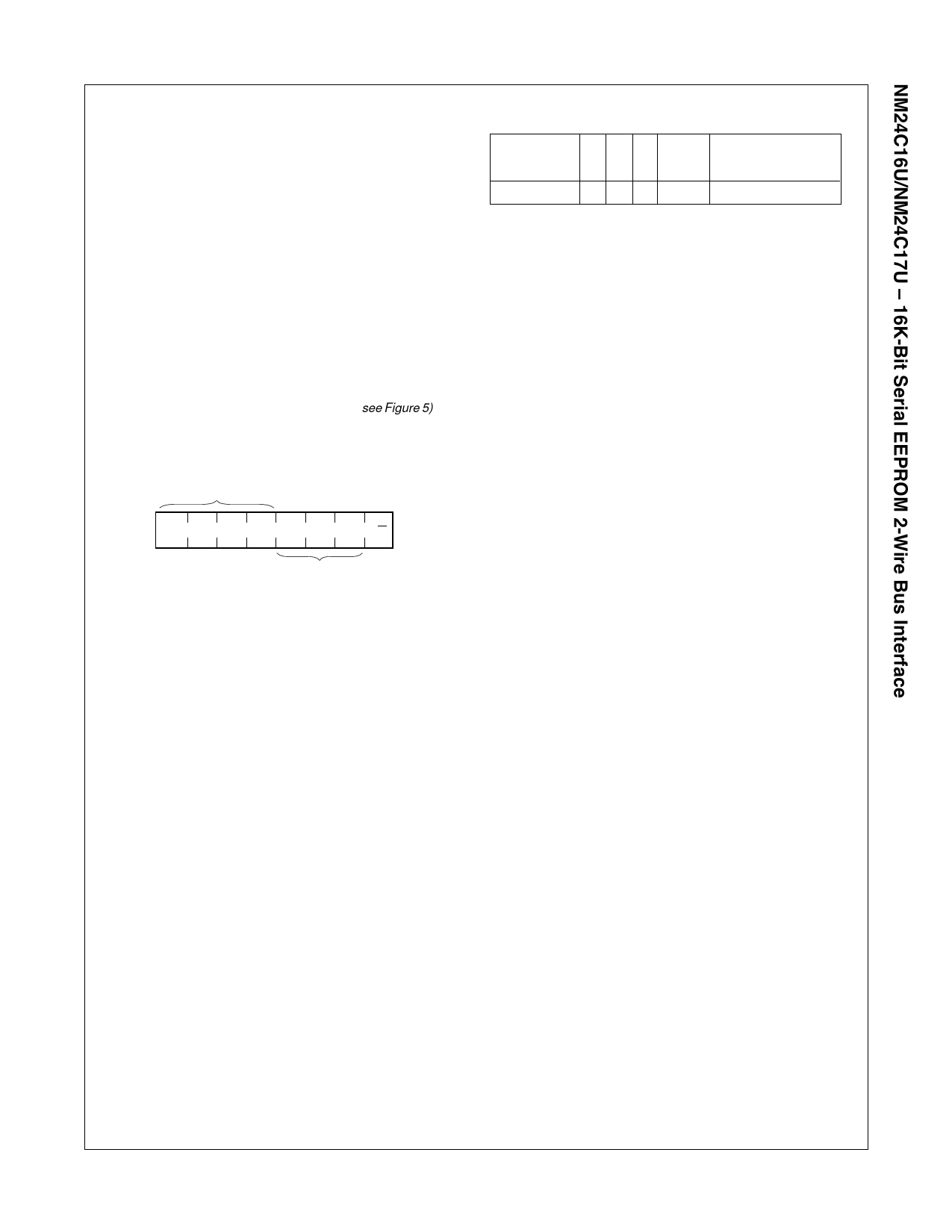

Slave Addresses (Figure 5)

Device Type

Identifier

Refer to the following table for Slave Addresses string details:

Device A0 A1 A2 Page Page Block

Blocks Addresses

NM24C16U/17U P P P 8 000 001 010 011 ... 111

P: Refers to an internal PAGE BLOCK memory segment.

All IIC EEPROMs use an internal protocol that defines a PAGE

BLOCK size of 2K bits (for Word addressess 0000 through 1111).

Therefore, address bits A0, A1, or A2 (if designated 'P') are used

to access a PAGE BLOCK in conjunction with the Word address

used to access any individual data byte (Word).

The last bit of the slave address defines whether a write or read

condition is requested by the master. A '1' indicates that a read

operation is to be executed, and a '0' initiates the write mode.

A simple review: After the NM24C16U/17U recognizes the start

condition, the devices interfaced to the IIC bus wait for a slave

address to be transmitted over the SDA line. If the transmitted

slave address matches an address of one of the devices, the

designated slave pulls the line LOW with an acknowledge signal

and awaits further transmissions.

1

01

NM24C16U/17U

0 A2 A1 A0 R/W (LSB)

Page

Block Address

DS800010-14

9

NM24C16U/17U Rev. B.1

www.fairchildsemi.com