W25S243AF-12 데이터 시트보기 (PDF) - Winbond

부품명

상세내역

일치하는 목록

W25S243AF-12 Datasheet PDF : 17 Pages

| |||

Preliminary W25S243A

64K × 64 BURST PIPELINED HIGH-SPEED

CMOS STATIC RAM

GENERAL DESCRIPTION

The W25S243A is a high-speed, low-power, synchronous-burst pipelined, CMOS static RAM

organized as 65,536 × 64 bits that operates on a single 3.3-volt power supply. A built-in two-bit burst

address counter supports both Pentium™ burst mode and linear burst mode. The mode to be

executed is controlled by the LBO pin. Pipelining or non-pipelining of the data outputs is controlled by

the FT pin. A snooze mode can reduces power dissipation.

This device supports 3-1-1-1-2-1-1-1 in a two-bank, back-to-back burst read cycle.

FEATURES

• Synchronous operation

• High-speed access time: 12 nS

• Single +3.3V power supply

• Individual byte write capability

• 3.3V LVTTL compatible I/O

• Clock-controlled and registered input

• Asynchronous output enable

• Pipelined/non-pipelined data output capability

• Supports snooze mode (low-power state)

• Internal burst counter supports Intel burst

(Interleaved) mode & linear burst mode

• Supports 2T/1T mode

• Packaged in 128-pin QFP and TQFP

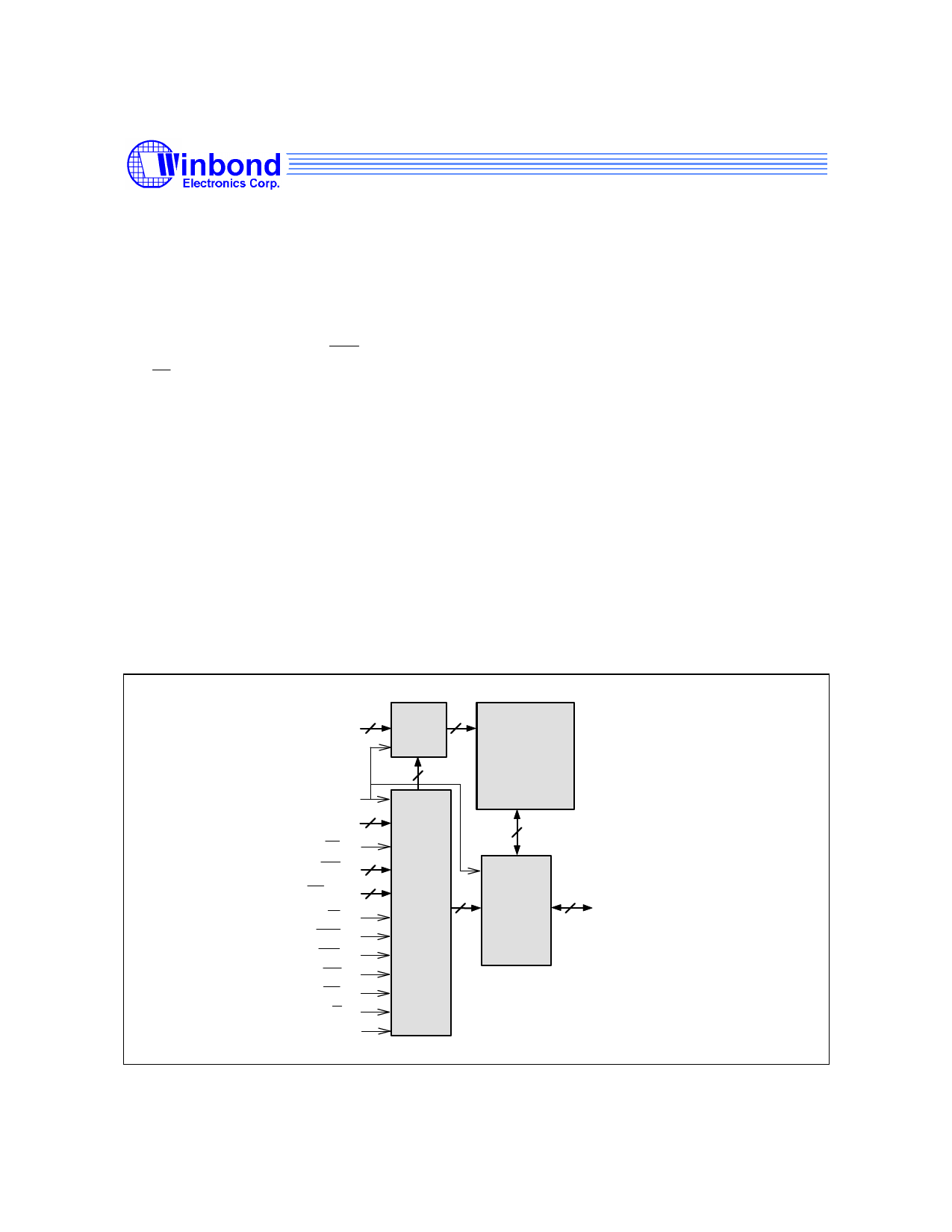

BLOCK DIAGRAM

A(15:0)

CLK

CE(3:1)

GW

BWE

BW(8:1)

OE

ADSC

ADSP

ADV

LBO

FT

ZZ

INPUT

REGISTER

CONTROL

LOGIC

REGISTER

64K X 64

CORE

ARRAY

DATA I/O

REGISTER

I/O(64:1)

Publication Release Date: November 1998

-1-

Revision A1