5962-8868101LA 데이터 시트보기 (PDF) - Austin Semiconductor

부품명

상세내역

일치하는 목록

5962-8868101LA Datasheet PDF : 11 Pages

| |||

Austin Semiconductor, Inc.

SRAM

MT5C2564

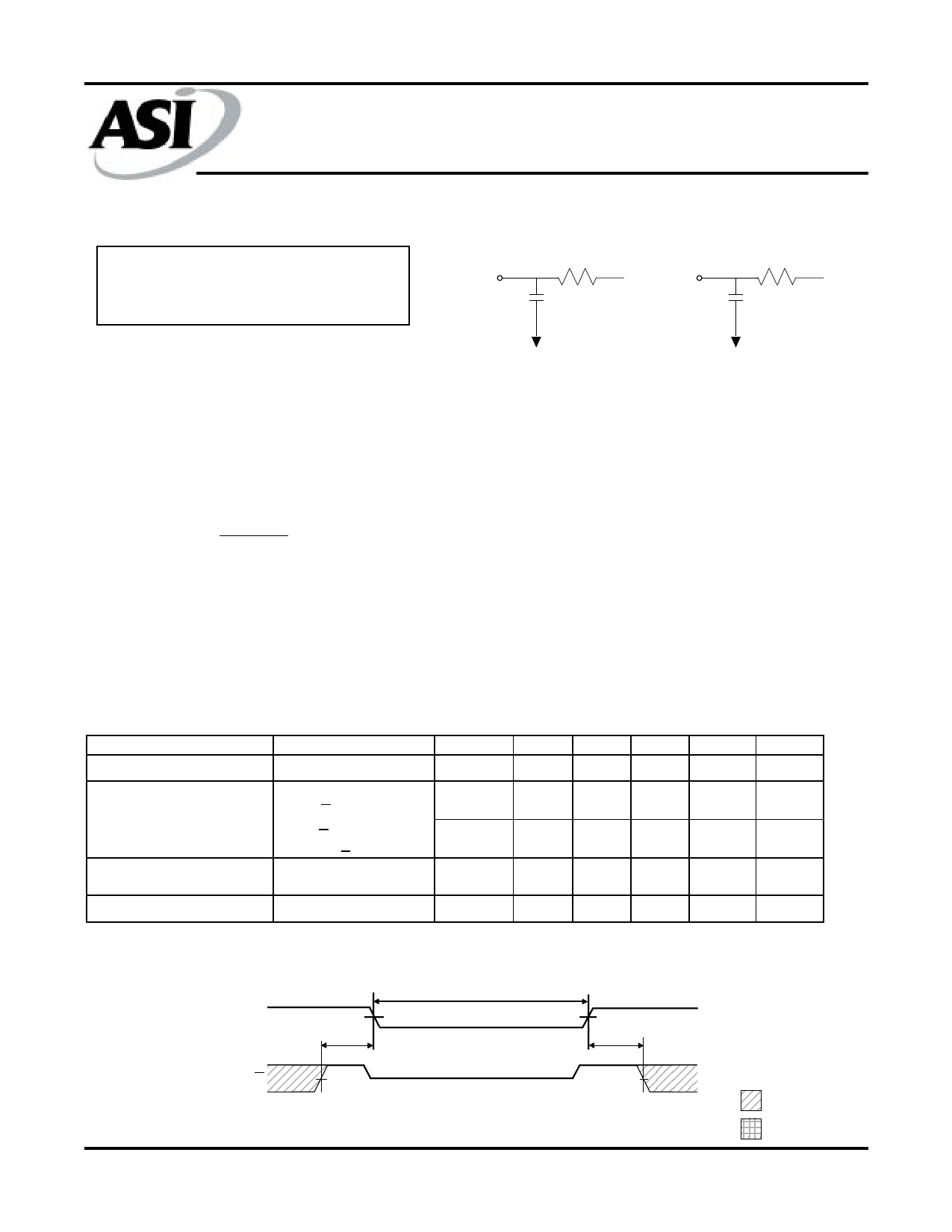

AC TEST CONDITIONS

Input pulse levels ...................................... Vss to 3.0V

Input rise and fall times ......................................... 5ns

Input timing reference levels ................................ 1.5V

Output reference levels ....................................... 1.5V

Output load ................................. See Figures 1 and 2

NOTES

1. All voltages referenced to VSS (GND).

2. -3V for pulse width < 20ns

3. ICC is dependent on output loading and cycle rates.

The specified value applies with the outputs

unloaded, and f = 1 Hz.

tRC (MIN)

4. This parameter is guaranteed but not tested.

5. Test conditions as specified with the output loading

as shown in Fig. 1 unless otherwise noted.

6. tLZCE, tLZWE, tLZOE, tHZCE, tHZOE and tHZWE are

specified with CL = 5pF as in Fig. 2. Transition is

measured ±200mV typical from steady state voltage,

167Ω

167Ω

Q

30pF VTH = 1.73V Q

5pF VTH = 1.73V

Fig. 1 Output Load

Equivalent

Fig. 2 Output Load

Equivalent

allowing for actual tester RC time constant.

7. At any given temperature and voltage condition,

tHZCE is less than tLZCE, and tHZWE is less than tLZWE and

tHZOE is less than tLZOE.

8. WE\ is HIGH for READ cycle.

9. Device is continuously selected. Chip enable is held in

its active state.

10. Address valid prior to, or coincident with, latest

occurring chip enable.

11. tRC = Read Cycle Time.

12. Chip enable (CE\) and write enable (WE\) can initiate and

terminate a WRITE cycle.

DATA RETENTION ELECTRICAL CHARACTERISTICS (L Version Only)

DESCRIPTION

CONDITIONS

SYM MIN MAX UNITS

VCC for Retention Data

VDR

2

---

V

Data Retention Current

CE\ > (VCC - 0.2V)

VIN > (VCC - 0.2V)

or < 0.2V

VCC = 2V ICCDR

VCC = 3V

1

mA

2

mA

Chip Deselect to Data

Retention Time

tCDR

0

---

ns

Operation Recovery Time

tR

tRC

ns

NOTES

4

4, 11

LOW Vcc DATA RETENTION WAVEFORM

MT5C2564

Rev. 2.0 11/00

VCC

tCDR

CE\

VIH

VIL

11112222333344445555666677778888

DATA RETENTION MODE

4.5V

VDR > 2V

4.5V

VDR

tR

11112222333344445555111166662222777733331111888844222244

111122223333DON’T CARE

1111222233334444UNDEFINED

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

5