M54HC40103(1993) 데이터 시트보기 (PDF) - STMicroelectronics

부품명

상세내역

일치하는 목록

M54HC40103 Datasheet PDF : 14 Pages

| |||

M54/M74HC40102/40103

DESCRIPTION (Continued)

When the ASYNCHRONOUS PRESET-ENABLE

(APE) input is low, data at the J inputs is asynchron-

ously forced into the counter regardless of the state

of the SPE, CI/CE, or CLOCK inputs. J Inputs J0-J7

represent two 4-bit BCD words for the HC40102 and

a single 8-bit binary word for the HC40103. When

the CLEAR (CLR input is low, the counter is asyn-

chronously cleared to its maximum count (9910 for

the HC40102 and 25510 for the HC40103 regard-

less of the state of any other input. The precedence

relationship between control input is indicated in the

truth table. If all control inputs are high at the time of

zero count, the counters will jump to the maximum

count, giving a counting sequence of 100 pr 256

clock pulses long. The HC40102 and HC40103 may

be cascaded using the CI/CE input and the CO/ZD

output, in either a synchronous or ripple mode. All

inputs are equipped with protection circuits against

static discharge and transient excess voltage.

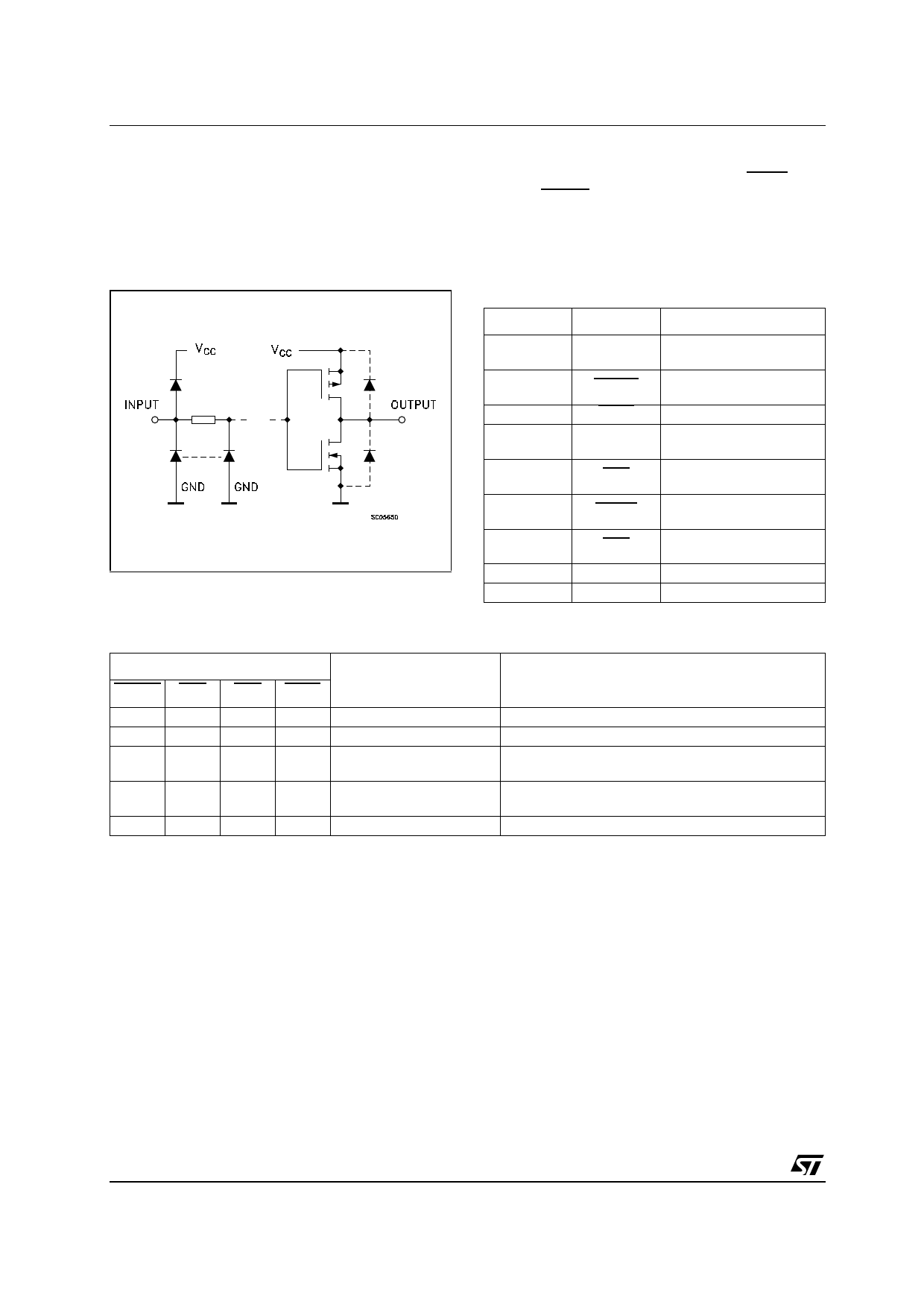

TRUTH TABLE

CONTROL INPUTS

CLEAR APE SPE CI/CE

MODE

FUNCTIONAL DESCRIPTION

H

H

H

H COUNT INHIBIT

EVEN IF CLOCK IS GIVEN, NO COUNT IS

MADE

H

H

H

L REGULAR COUNT

DOWN COUNT AT RISING EDGE OF CLOCK

H

H

L

X SYNCHRONOUS PRESET DATA OF PI TERMINAL IS PRESET AT

RISING EDGE OF CLOCK

H

L

X

X ASYNCRONOUS PRESET DATA PF PI TERMINAL IS

ASYNCHRONOUSLY PRESET TO CLOCK

L

X

X

X CLEAR

COUNTER IS SET TO MAXIMUM COUNT

X: DON’T CARE - MAXIMUM COUNT: ”99” FOR HC40102 AND ”255”: FOR HC40103

LOGIC DIAGRAM (HC40102)

2/14