YMF752-S 데이터 시트보기 (PDF) - Yamaha Corporation

부품명

상세내역

일치하는 목록

YMF752-S Datasheet PDF : 14 Pages

| |||

YMF752

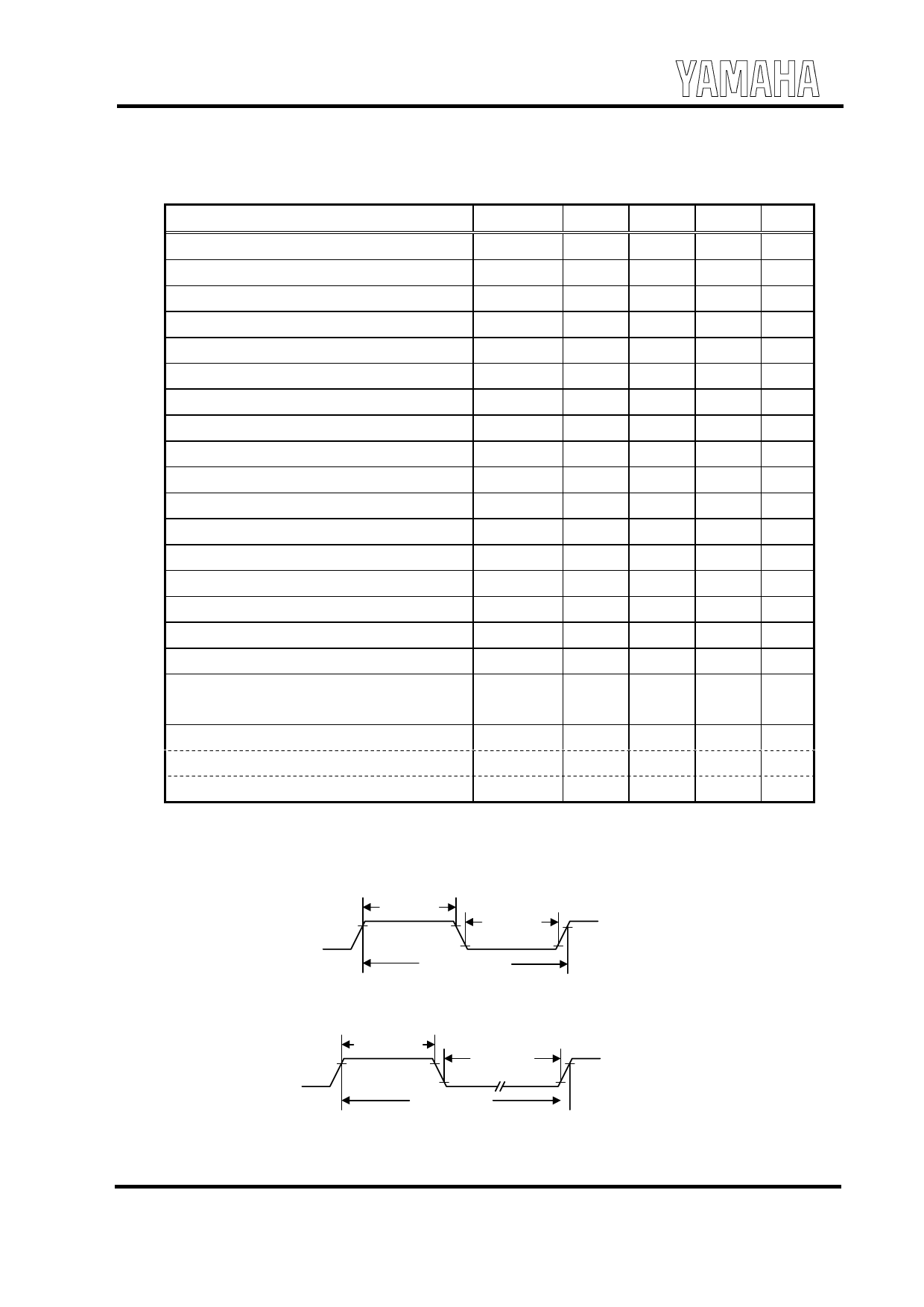

4-2. AC-link Interface

Parameter

Symbol Min.

BIT_CLK clock period

Tclk_period -

BIT_CLK low pulse width

Tclk_low 36.0

BIT_CLK high pulse width

Tclk_high 36.0

BIT_CLK rise time

Trise_clk

-

BIT_CLK fall time

Tfall_clk

-

SYNC period

Tsync_period -

SYNC low pulse width

Tsync_low

-

SYNC high pulse width

Tsync_high -

SYNC rise time

Trise_sync

-

SYNC fall time

Tfall_sync

-

SDATA_IN, SDATA_OUT setup time

Tsetup

10.0

SDATA_IN, SDATA_OUT hold time

Thold

10.0

SDATA_IN delay time

Tdelay

-

SDATA_IN rise time

Trise_din

-

SDATA_IN fall time

Tfall_din

-

SDATA_OUT rise time

Trise_dout

-

SDATA_OUT fall time

Tfall_dout

-

AC-link Low Power Mode

Ts2_pdwn

-

End of slot 2 to BIT_CLK, SDATA_IN low

Active Test Mode

Setup to trailing edge of RESET#

Tsetup2rst 15.0

Rising edge of RESET# to Hi-Z

Toff

-

Note) TOP=25°C, AVDD=5.0V, Capacitor load=50pF

Typ.

81.38

40.7

40.7

-

-

20.8

19.5

1.3

-

-

-

-

-

-

-

-

-

-

-

-

Max. Unit

-

ns

45.0 ns

45.0 ns

6

ns

6

ns

-

µs

-

µs

-

µs

6

ns

6

ns

-

ns

-

ns

15.0 ns

6

ns

6

ns

6

ns

6

ns

1.0

µs

-

ns

50

ns

BIT_CLK

BIT_CLK

SYNC

Tclk_high

Tclk_low

Tclk_period

SYNC

Tsync_high

Tsync_low

Tsync_period

10

July 2, 1999